- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371098 > MF0128M-05AAxx (Mitsubishi Electric Corporation) GT 9C 3#12 6#16 SKT PLUG PDF資料下載

參數(shù)資料

| 型號(hào): | MF0128M-05AAxx |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | GT 9C 3#12 6#16 SKT PLUG |

| 中文描述: | 16位產(chǎn)品數(shù)據(jù)總線CF卡 |

| 文件頁數(shù): | 4/32頁 |

| 文件大小: | 589K |

| 代理商: | MF0128M-05AAXX |

第1頁第2頁第3頁當(dāng)前第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

MITSUBISHI STORAGE CARD

Preliminary

MF0XXXX-05AAXX series

CompactFlash CARDS

MITSUBISHI

ELECTRIC

4 June.2001

. Rev. 1.3

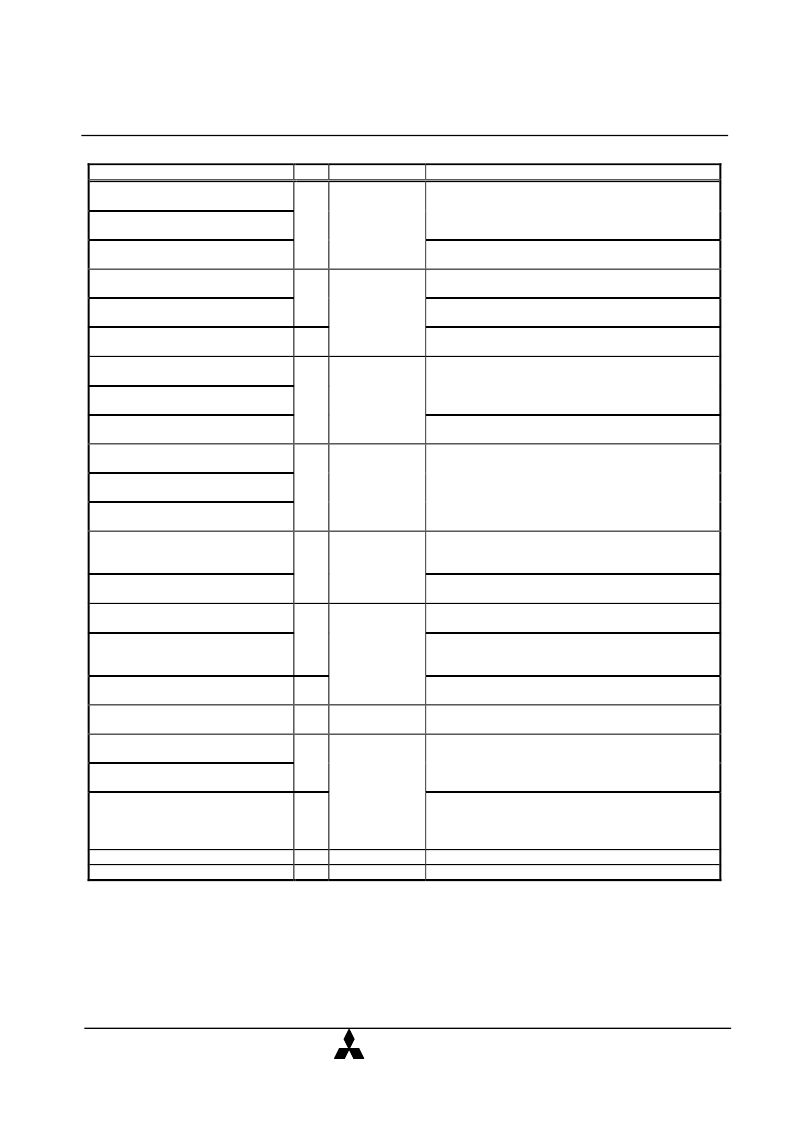

Signal Description(Continued)

Signal Name

Attribute Memory Select[REG#]

(PC Card Memory Mode)

Attribute Memory Select[REG#]

(PC Card I/O Mode)

Attribute Memory Select[REG#]

(True IDE Interface)

Battery Voltage Detect[BVD2]

(PC Card Memory Mode)

Audio Digital Waveform[SPKR#]

(PC Card I/O Mode)

DASP#

(True IDE Interface)

Card Reset[RESET]

(PC Card Memory Mode)

Card Reset[RESET]

(PC Card I/O Mode)

Card Reset[RESET#]

(True IDE Interface)

Wait[WAIT#]

(PC card Memory Mode)

Wait[WAIT#]

(PC card I/O Mode)

IORDY

(True IDE Interface)

Input Port Acknowledge[INPACK#]

(PC Card I/O Mode)

Input Port Acknowledge[INPACK#]

(True IDE Interface)

Battery Voltage Detect[BVD1]

(PC Card Memory Mode)

STSCHG#

(PC Card I/O Mode)

I/O

I

Pin No.

Description

When this signal is asserted, access is limited to

Attribute Memory with OE#/WE# and I/O Space

with IORD#/IOWR#.

44

This input signal is not used for this mode and

should be connected to Vcc by the host.

This output is driven to a high-level.

O

SPKR# is kept negated because this Card does not

have digital audio output.

This signal is the DISK Active/Slave Present signal

in the Master/Slave handshake protocol.

By assertion of this signal, all registers of this Card

are cleared. This signal should be kept to High-Z or

High Level by the host for at least 1ms after Vcc

applied.

This input pin is the active low hardware reset from

the host.

This signal is asserted to delay completion of the

memory or I/O access cycle.

I/O

45

I

41

O

42

This signal is asserted when the Card is selected

and can respond to an I/O Read cycle at the

address on the address bus.

This signal is not used for this mode and should not

be connected at the host.

This output is driven to a high-level.

O

43

O

This signal is asserted low to alert the host to

changes in the status of Configuration Status

Register in the Attribute Memory Space.

This signal is the Pass Diagnostic signal in the

Master/Slave handshake protocol.

VS1 is grounded so that the Card CIS can be read

at 3.3V and VS2 is N.C.

This signal is not used for this mode.

PDIAG#

(True IDE Interface)

Voltage Sense[VS1, VS2]

Cable Select[CSEL]

(PC Card Memory Mode)

Cable Select[CSEL]

(PC Card I/O Mode)

Cable Select[CSEL]

(True IDE Interface)

I/O

46

O

33, 40

-

I

39

This signal is used to configure this Card as a

Master or a Slave. When this signal is grounded,

this Card is configured as a Master. When this

signal is Open, this Card is configured as a Slave.

5V or 3.3V power.

Ground.

Vcc

GND

-

-

13, 38

1, 50

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MF0032M-05AAXX | GT 5C 5#16S SKT PLUG |

| MF0256M-07BTxx | 8/16-bit Data Bus Flash ATA PC Card |

| MF0064M-07BTXX | 8/16-bit Data Bus Flash ATA PC Card |

| MF0064M-07ATXX | 8/16-bit Data Bus Flash ATA PC Card |

| MF0256M-07ATxx | 8/16-bit Data Bus Flash ATA PC Card |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MF0128M-07ATXX | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:8/16-bit Data Bus Flash ATA PC Card |

| MF0128M-07BTXX | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:8/16-bit Data Bus Flash ATA PC Card |

| MF0128M-11ATXX | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:8/16-bit Data Bus Flash ATA PC Card |

| MF01320A | 制造商:SMC Corporation of America 功能描述: |

| MF0192M-11ATXX | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:8/16-bit Data Bus Flash ATA PC Card |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。