- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25639 > MD80C52TXXX-12/883D (TEMIC SEMICONDUCTORS) 8-BIT, MROM, 12 MHz, MICROCONTROLLER, CDIP40 PDF資料下載

參數(shù)資料

| 型號(hào): | MD80C52TXXX-12/883D |

| 廠商: | TEMIC SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, CDIP40 |

| 文件頁數(shù): | 8/46頁 |

| 文件大小: | 7004K |

| 代理商: | MD80C52TXXX-12/883D |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當(dāng)前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁

140

7593L–AVR–09/12

AT90USB64/128

Bit 2:0 – CSn2:0: Clock Select

The three clock select bits select the clock source to be used by the Timer/Counter, see Figure

If external pin modes are used for the Timer/Countern, transitions on the Tn pin will clock the

counter even if the pin is configured as an output. This feature allows software control of the

counting.

15.10.5

TCCR1C – Timer/Counter1 Control Register C

15.10.6

TCCR3C – Timer/Counter3 Control Register C

Bit 7 – FOCnA: Force Output Compare for Channel A

Bit 6 – FOCnB: Force Output Compare for Channel B

Bit 5 – FOCnC: Force Output Compare for Channel C

The FOCnA/FOCnB/FOCnC bits are only active when the WGMn3:0 bits specifies a non-PWM

mode. When writing a logical one to the FOCnA/FOCnB/FOCnC bit, an immediate compare

match is forced on the waveform generation unit. The OCnA/OCnB/OCnC output is changed

according to its COMnx1:0 bits setting. Note that the FOCnA/FOCnB/FOCnC bits are imple-

mented as strobes. Therefore it is the value present in the COMnx1:0 bits that determine the

effect of the forced compare.

A FOCnA/FOCnB/FOCnC strobe will not generate any interrupt nor will it clear the timer in Clear

Timer on Compare Match (CTC) mode using OCRnA as TOP.

The FOCnA/FOCnB/FOCnB bits are always read as zero.

Bit 4:0 – Reserved bits

These bits are reserved for future use. For ensuring compatibility with future devices, these bits

must be written to zero when TCCRnC is written.

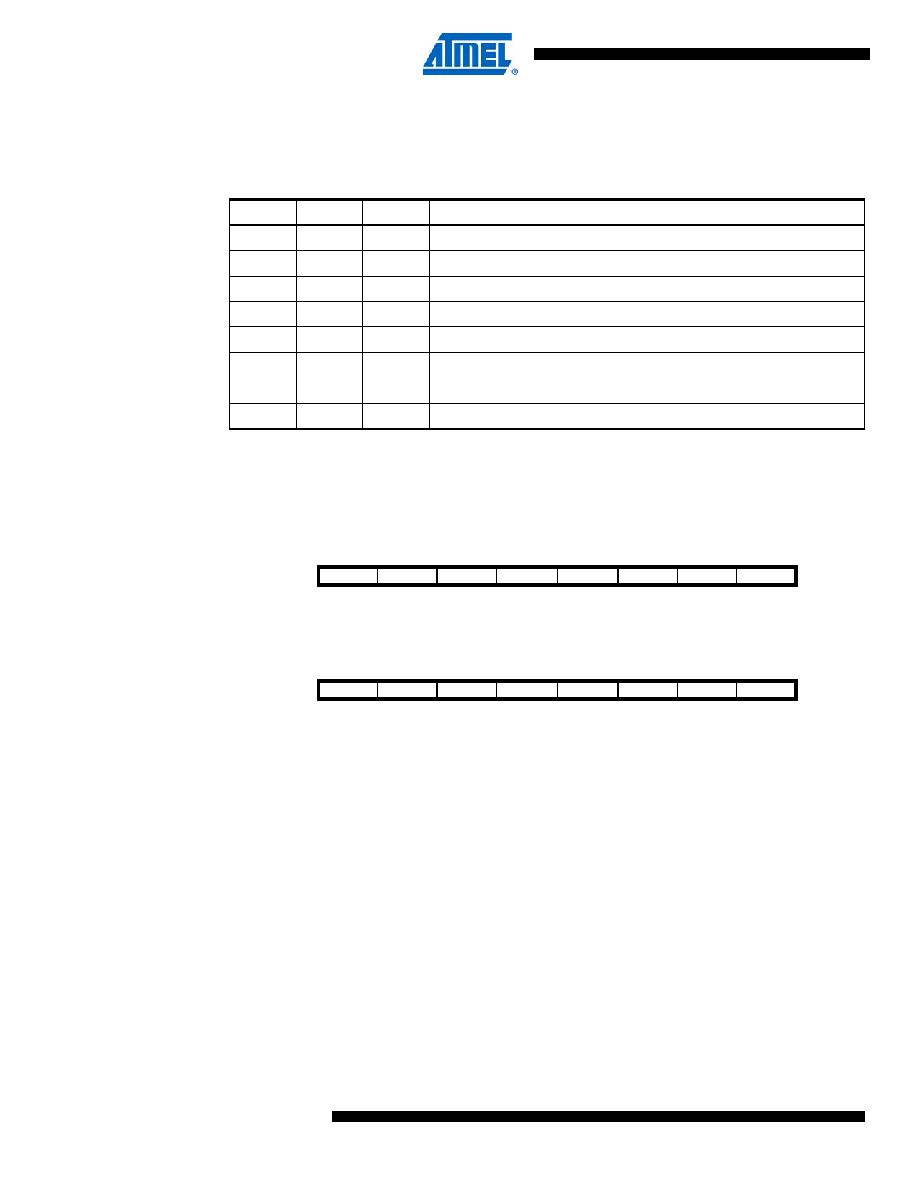

Table 15-5.

Clock Select bit description.

CSn2

CSn1

CSn0

Description

0

No clock source. (Timer/Counter stopped)

00

1

clk

I/O/1 (no prescaling

01

0

clkI/O/8 (from prescaler)

01

1

clkI/O/64 (from prescaler)

10

0

clk

I/O/256 (from prescaler)

10

1

clkI/O/1024 (from prescaler)

1

0

External clock source on Tn pin. Clock on falling edge

1

External clock source on Tn pin. Clock on rising edge

Bit

7

6

5

4

3

210

FOC1A

FOC1B

FOC1C

–

TCCR1C

Read/write

W

R

RRR

Initial value

0

Bit

7

6

5

4

3

210

FOC3A

FOC3B

FOC3C

–

TCCR3C

Read/write

W

R

RRR

Initial value

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC80C52CXXX-12SHXXX:D | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, CDIP40 |

| MD80C52EXXX-16/883:D | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, CDIP40 |

| MD80C52EXXX-30 | 8-BIT, MROM, 30 MHz, MICROCONTROLLER, CDIP40 |

| MD80C52XXX-12SHXXX:D | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, CDIP40 |

| MD80C52XXX-36MQ | 8-BIT, MROM, 36 MHz, MICROCONTROLLER, CDIP40 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MD80C86 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:CMOS 16-Bit Microprocessor |

| MD80C862 | 制造商:Intel 功能描述:PROCESSOR:MICRO-PROCESSOR |

| MD80C86-2 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:CMOS 16-Bit Microprocessor |

| MD80C86-2/883 | 制造商:Intersil Corporation 功能描述:MPU 16BIT CMOS 8MHZ 40CDIP - Rail/Tube 制造商:Rochester Electronics LLC 功能描述:CPU 16BILT 5V CMOS 8MHZ 40CDIP - Bulk |

| MD80C86-2/B | 制造商:Intersil Corporation 功能描述:MPU 16BIT CMOS 8MHZ 40CDIP - Rail/Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。