- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄9323 > MCP4331T-502E/ML (Microchip Technology)IC DGTL POT QUAD 5K 20QFN PDF資料下載

參數(shù)資料

| 型號(hào): | MCP4331T-502E/ML |

| 廠商: | Microchip Technology |

| 文件頁數(shù): | 2/35頁 |

| 文件大小: | 0K |

| 描述: | IC DGTL POT QUAD 5K 20QFN |

| 標(biāo)準(zhǔn)包裝: | 3,300 |

| 接片: | 129 |

| 電阻(歐姆): | 5k |

| 電路數(shù): | 4 |

| 溫度系數(shù): | 標(biāo)準(zhǔn)值 150 ppm/°C |

| 存儲(chǔ)器類型: | 易失 |

| 接口: | 4 線 SPI(芯片選擇) |

| 電源電壓: | 1.8 V ~ 5.5 V |

| 工作溫度: | -40°C ~ 125°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 20-VFQFN 裸露焊盤 |

| 供應(yīng)商設(shè)備封裝: | 20-QFN 裸露焊盤(4x4) |

| 包裝: | 帶卷 (TR) |

第1頁當(dāng)前第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁

MCP433X/435X

DS22242A-page 10

2010 Microchip Technology Inc.

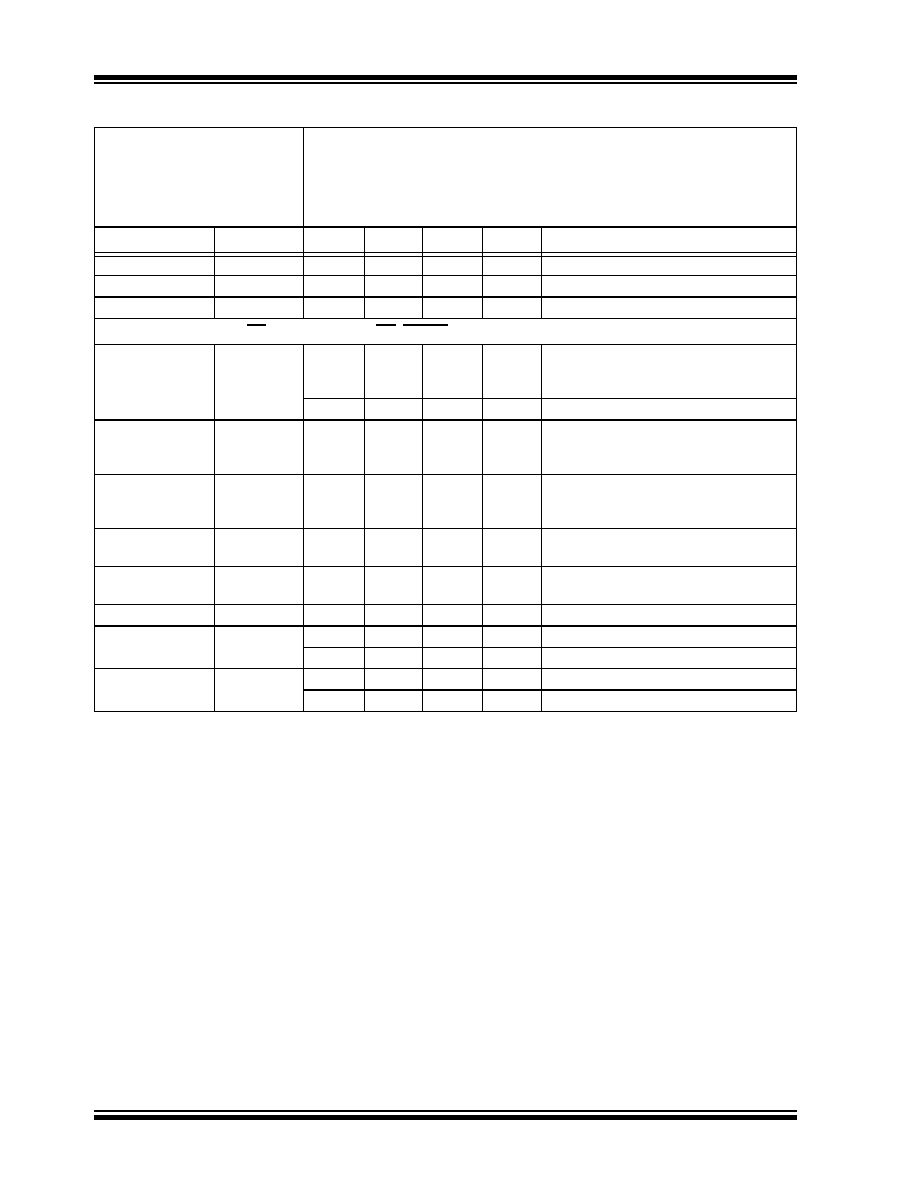

Capacitance (PA)CAW

—

75

—

pF

f =1 MHz, Code = Full Scale

Capacitance (Pw)CW

—

120

—

pF

f =1 MHz, Code = Full Scale

Capacitance (PB)CBW

—

75

—

pF

f =1 MHz, Code = Full Scale

Digital Inputs/Outputs (CS, SDI, SDO, SCK, WP, RESET)

Schmitt Trigger

High Input

Threshold

VIH

0.45 VD

D

——

V

2.7V

VDD 5.5V

(Allows 2.7V Digital VDD with

5V Analog VDD)

0.5 VDD

——

V

1.8V

VDD 2.7V

Schmitt Trigger

Low Input

Threshold

VIL

——

0.2VDD

V

Hysteresis of

Schmitt Trigger

Inputs

VHYS

—0.1VDD

—V

High Voltage Input

Entry Voltage

VIHH

8.5

—

12.5 (6)

V

High Voltage Input

Exit Voltage

VIHH

——

VDD +

0.8V

V

High Voltage Limit

VMAX

——

12.5 (6)

V

Pin can tolerate VMAX or less.

Output Low

Voltage (SDO)

VOL

VSS

—0.3VDD

VIOL = 5 mA, VDD = 5.5V

VSS

—0.3VDD

VIOL = 1 mA, VDD = 1.8V

Output High

Voltage (SDO)

VOH

0.7VDD

—VDD

VIOH = -2.5 mA, VDD = 5.5V

0.7VDD

—VDD

VIOL = -1 mA, VDD = 1.8V

AC/DC CHARACTERISTICS (CONTINUED)

DC Characteristics

Standard Operating Conditions (unless otherwise specified)

Operating Temperature

–40°C

TA +125°C (extended)

All parameters apply across the specified operating ranges unless noted.

VDD = +2.7V to 5.5V, 5 k, 10 k, 50 k, 100 k devices.

Typical specifications represent values for VDD = 5.5V, TA = +25°C.

Parameters

Sym

Min

Typ

Max

Units

Conditions

Note 1:

Resistance is defined as the resistance between terminal A to terminal B.

2:

INL and DNL are measured at VW with VA = VDD and VB = VSS.

3:

MCP43X1 only.

4:

MCP43X2 only, includes VWZSE and VWFSE.

5:

Resistor terminals A, W and B’s polarity with respect to each other is not restricted.

6:

This specification by design.

7:

Non-linearity is affected by wiper resistance (RW), which changes significantly over voltage and

temperature.

8:

The MCP43X1 is externally connected to match the configurations of the MCP43X2, and then tested.

9:

POR/BOR is not rate dependent.

10: Supply current is independent of current through the resistor network.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DS1248WP-120 | IC NVSRAM 1MBIT 120NS 34PCM |

| VI-2NL-MY-F2 | CONVERTER MOD DC/DC 28V 50W |

| MCP4251-502E/SL | IC DGTL POT 5K 2CH 14SOIC |

| DS1248YP-70 | IC NVSRAM 1MBIT 70NS 34PCM |

| MCP4331T-104E/ST | IC DGTL POT QUAD 100K 20TSSOP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MCP4331T-503E/ML | 功能描述:數(shù)字電位計(jì) IC 50k SPI 7-bit Quad Channel RoHS:否 制造商:Maxim Integrated 電阻:200 Ohms 溫度系數(shù):35 PPM / C 容差:25 % POT 數(shù)量:Dual 每 POT 分接頭:256 弧刷存儲(chǔ)器:Volatile 緩沖刷: 數(shù)字接口:Serial (3-Wire, SPI) 描述/功能:Dual Volatile Low Voltage Linear Taper Digital Potentiometer 工作電源電壓:1.7 V to 5.5 V 電源電流:27 uA 最大工作溫度:+ 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TQFN-16 封裝:Reel |

| MCP4331T-503E/ST | 功能描述:數(shù)字電位計(jì) IC 50k SPI 7-bit Quad Channel RoHS:否 制造商:Maxim Integrated 電阻:200 Ohms 溫度系數(shù):35 PPM / C 容差:25 % POT 數(shù)量:Dual 每 POT 分接頭:256 弧刷存儲(chǔ)器:Volatile 緩沖刷: 數(shù)字接口:Serial (3-Wire, SPI) 描述/功能:Dual Volatile Low Voltage Linear Taper Digital Potentiometer 工作電源電壓:1.7 V to 5.5 V 電源電流:27 uA 最大工作溫度:+ 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TQFN-16 封裝:Reel |

| MCP4332-103E/ST | 功能描述:數(shù)字電位計(jì) IC 10k SPI Qd Ch 7-Bit Volatile memory RoHS:否 制造商:Maxim Integrated 電阻:200 Ohms 溫度系數(shù):35 PPM / C 容差:25 % POT 數(shù)量:Dual 每 POT 分接頭:256 弧刷存儲(chǔ)器:Volatile 緩沖刷: 數(shù)字接口:Serial (3-Wire, SPI) 描述/功能:Dual Volatile Low Voltage Linear Taper Digital Potentiometer 工作電源電壓:1.7 V to 5.5 V 電源電流:27 uA 最大工作溫度:+ 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TQFN-16 封裝:Reel |

| MCP4332-104E/ST | 功能描述:數(shù)字電位計(jì) IC 100k SPI Qd Ch 7-Bit Volatile memory RoHS:否 制造商:Maxim Integrated 電阻:200 Ohms 溫度系數(shù):35 PPM / C 容差:25 % POT 數(shù)量:Dual 每 POT 分接頭:256 弧刷存儲(chǔ)器:Volatile 緩沖刷: 數(shù)字接口:Serial (3-Wire, SPI) 描述/功能:Dual Volatile Low Voltage Linear Taper Digital Potentiometer 工作電源電壓:1.7 V to 5.5 V 電源電流:27 uA 最大工作溫度:+ 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TQFN-16 封裝:Reel |

| MCP4332-502E/ST | 功能描述:數(shù)字電位計(jì) IC 5k SPI Qd Ch 7-Bit Volatile memory RoHS:否 制造商:Maxim Integrated 電阻:200 Ohms 溫度系數(shù):35 PPM / C 容差:25 % POT 數(shù)量:Dual 每 POT 分接頭:256 弧刷存儲(chǔ)器:Volatile 緩沖刷: 數(shù)字接口:Serial (3-Wire, SPI) 描述/功能:Dual Volatile Low Voltage Linear Taper Digital Potentiometer 工作電源電壓:1.7 V to 5.5 V 電源電流:27 uA 最大工作溫度:+ 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TQFN-16 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。