- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371083 > MCM62110 (Motorola, Inc.) 32K x 9 Bit Synchronous Dual I/O or Separate I/O Fast Static RAM with Parity Checker PDF資料下載

參數(shù)資料

| 型號(hào): | MCM62110 |

| 廠商: | Motorola, Inc. |

| 英文描述: | 32K x 9 Bit Synchronous Dual I/O or Separate I/O Fast Static RAM with Parity Checker |

| 中文描述: | 32K的× 9位同步雙I / O或具有奇偶校驗(yàn)檢查分離I / O快速靜態(tài)存儲(chǔ)器 |

| 文件頁數(shù): | 3/12頁 |

| 文件大小: | 206K |

| 代理商: | MCM62110 |

MCM62110

3

MOTOROLA FAST SRAM

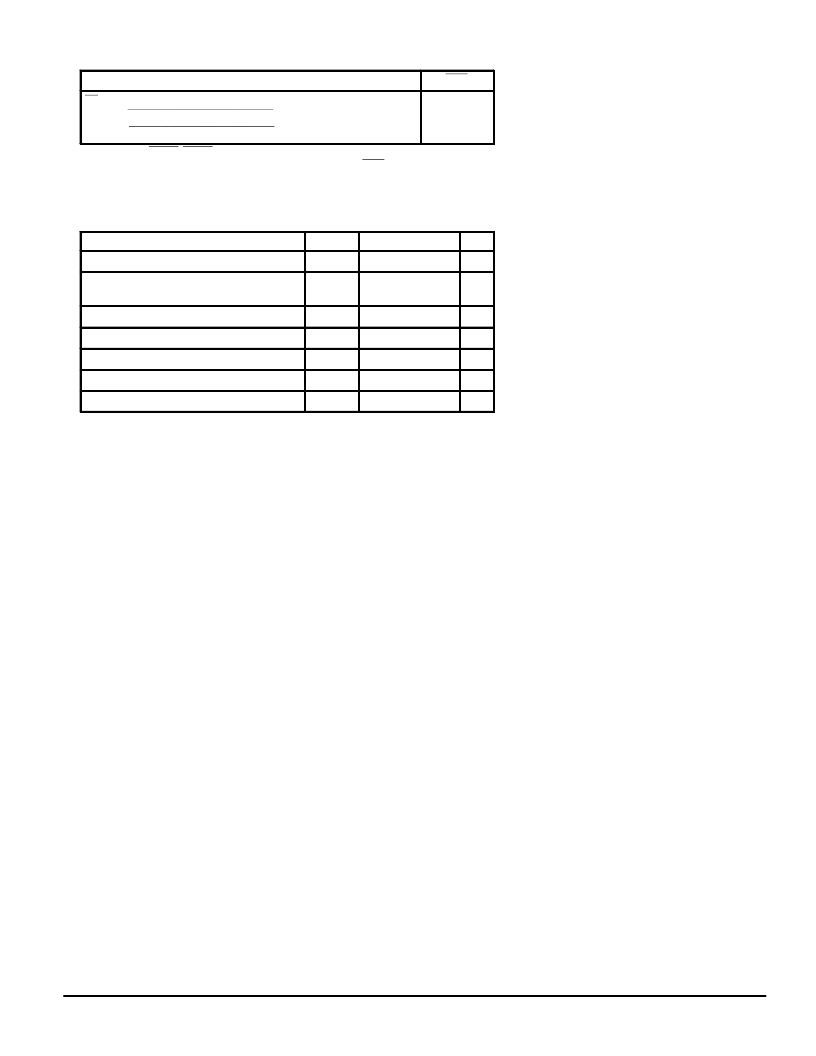

Parity Scheme

DPE

E1 = VIH and/or E2 = VIL

RAMP = RAM0

⊕

RAM1

⊕

. . .

⊕

RAM7

RAMP

≠

RAM0

⊕

RAM1

⊕

. . .

⊕

RAM7

1

1

0

NOTE: RAMP, RAM0, RAM1 . . . , refer to the data that is present on the RAMs internal bus,

not necessarily data that resides in the RAM array. DPE is always delayed one

clock, and is registered on the rising edge of K at the beginning of the following clock

cycle (see AC CHARACTERISTICS).

ABSOLUTE MAXIMUM RATINGS

(Voltages Referenced to VSS = VSSQ = 0 V)

Rating

Symbol

Value

Unit

Power Supply

VCC

– 0.5 to + 7.0

V

Voltage Relative to VSS/VSSQ for Any

Pin Except VCC and VCCQ

Vin, Vout

– 0.5 to VCC + 0.5

V

Output Current (per I/O)

Iout

±

20

mA

Power Dissipation

PD

1.2

W

Temperature Under Bias

Tbias

– 10 to + 85

°

C

Operating Temperature

TA

0 to +70

°

C

Storage Temperature

Tstg

– 55 to + 125

°

C

NOTE: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are

exceeded. Functional operation should be restricted to RECOMMENDED OPER-

ATING CONDITIONS. Exposure to higher than recommended voltages for

extended periods of time could affect device reliability.

This device contains circuitry to protect the

inputs against damage due to high static volt-

ages or electric fields; however, it is advised

that normal precautions be taken to avoid

application of any voltage higher than maxi-

mum rated voltages to this high–impedance

circuit.

This CMOS memory circuit has been

designed to meet the dc and ac specifications

shown in the tables, after thermal equilibrium

has been established.

This device contains circuitry that will

ensure the output devices are in High–Z at

power up.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MCM62110FN15 | 32K x 9 Bit Synchronous Dual I/O or Separate I/O Fast Static RAM with Parity Checker |

| MCM62110FN17 | CAP CERM 10PF 200V NP0 RF 0603 |

| MCM62110FN20 | 32K x 9 Bit Synchronous Dual I/O or Separate I/O Fast Static RAM with Parity Checker |

| MCM6226BB | 128K x 8 Bit Static Random Access Memory |

| MCM6226BBXJ35R2 | 128K x 8 Bit Static Random Access Memory |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MCM62110FN15 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:32K x 9 Bit Synchronous Dual I/O or Separate I/O Fast Static RAM with Parity Checker |

| MCM62110FN17 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:32K x 9 Bit Synchronous Dual I/O or Separate I/O Fast Static RAM with Parity Checker |

| MCM62110FN20 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:32K x 9 Bit Synchronous Dual I/O or Separate I/O Fast Static RAM with Parity Checker |

| MCM6223YJ15 | 制造商:Motorola Inc 功能描述: |

| MCM6226BAXJ20 | 制造商:Motorola Inc 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。