- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄201872 > MCF51QH64VHS (FREESCALE SEMICONDUCTOR INC) FLASH, 50 MHz, MICROCONTROLLER, QCC44 PDF資料下載

參數(shù)資料

| 型號(hào): | MCF51QH64VHS |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | FLASH, 50 MHz, MICROCONTROLLER, QCC44 |

| 封裝: | 5 X 5 MM, QFN-44 |

| 文件頁(yè)數(shù): | 31/72頁(yè) |

| 文件大小: | 1031K |

| 代理商: | MCF51QH64VHS |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)當(dāng)前第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)

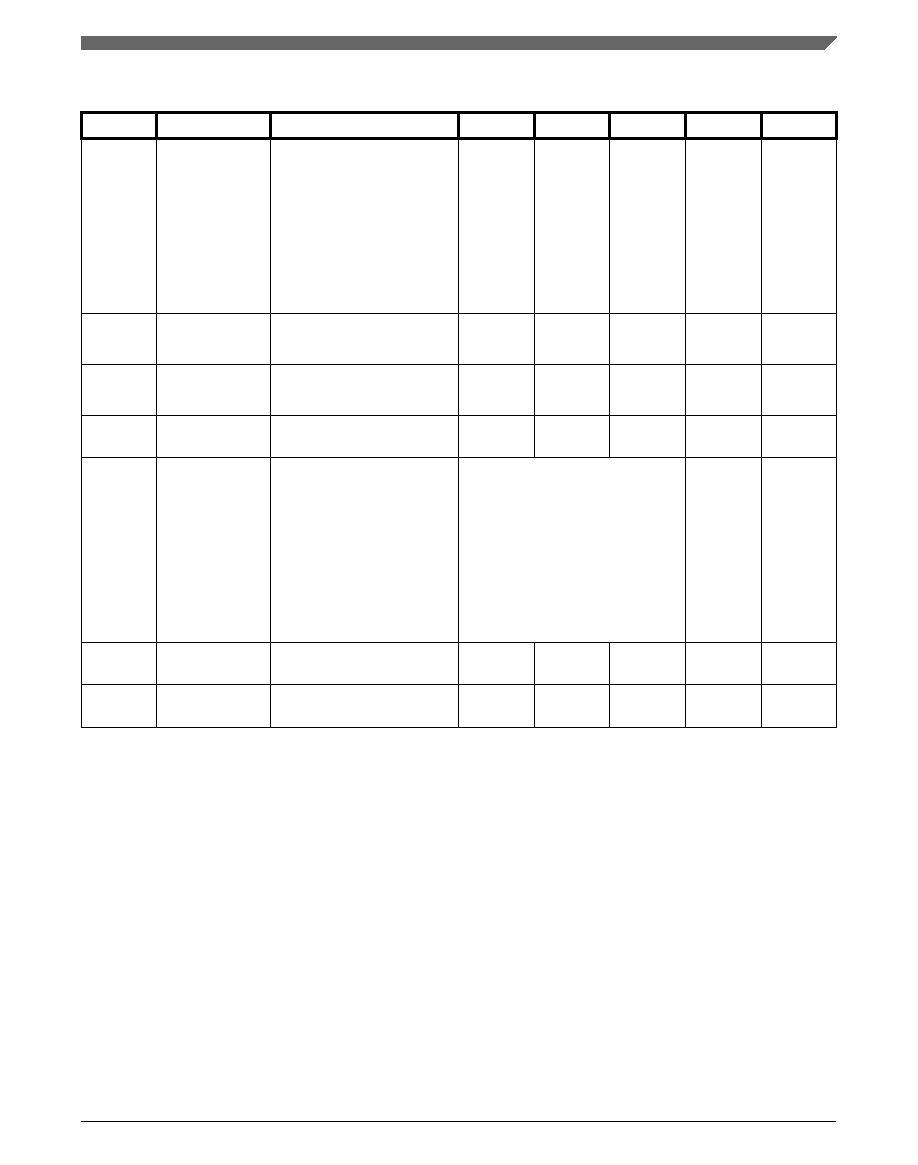

Table 24. 12-bit ADC characteristics (VREFH = VDDA, VREFL = VSSA) (continued)

Symbol

Description

Min.

Typ.2

Max.

Unit

Notes

DNL

Differential non-

linearity

12 bit modes

<12 bit modes

±0.7

±0.2

±TBD

±0.5

LSB4

ADC

conversion

clock

<12MHz,

Max

hardware

averaging

(AVGE =

%1, AVGS

= %11)

INL

Integral non-

linearity

12 bit modes

<12 bit modes

±0.5

±TBD

LSB4

Max

averaging

EFS

Full-scale error

12 bit modes

<12 bit modes

±0.4

LSB4

VADIN =

VDDA

EQ

Quantization

error

12 bit modes

—

±0.5

LSB4

EIL

Input leakage

error

IIn × RAS

mV

IIn =

leakage

current

(refer to

the MCU's

voltage

and

current

operating

ratings)

Temp sensor

slope

–40°C to 105°C

—

TBD

—

mV/°C

VTEMP25

Temp sensor

voltage

25°C

—

TBD

—

mV

1. All accuracy numbers assume the ADC is calibrated with VREFH = VDDA

2. Typical values assume VDDA = 3.0 V, Temp = 25°C, fADCK = 2.0 MHz unless otherwise stated. Typical values are for

reference only and are not tested in production.

3. The ADC supply current depends on the ADC conversion clock speed, conversion rate and the ADLPC bit (low power).

For lowest power operation the ADLPC bit should be set, the HSC bit should be clear with 1MHz ADC conversion clock

speed.

4. 1 LSB = (VREFH - VREFL)/2N

Figure TBD

Figure 10. Typical TUE vs. ADC conversion rate 12-bit single-ended mode

Analog

MCF51JF128 Advance Information Data Sheet, Rev. 3, 08/2011.

Freescale Semiconductor, Inc.

Preliminary

37

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MB95F563HPFT-G-JNE2 | 8-BIT, FLASH, 16.25 MHz, MICROCONTROLLER, PDSO20 |

| MB95F563HWQN-G-JNERE1 | 8-BIT, FLASH, 16.25 MHz, MICROCONTROLLER, PQCC32 |

| MB95F563KPFT-G-JNE2 | 8-BIT, FLASH, 16.25 MHz, MICROCONTROLLER, PDSO20 |

| MSP430G2152IN20 | 16-BIT, FLASH, 16 MHz, RISC MICROCONTROLLER, PDIP20 |

| MSP430G2152IPW14 | 16-BIT, FLASH, 16 MHz, RISC MICROCONTROLLER, PDSO14 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MCF51QH64VLF | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Advance Information Temperature range (ambient): -40°C to 105°C |

| MCF51QM128 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:MCF51QM128 |

| MCF51QM128_12 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:MCF51QM128 |

| MCF51QM128VHS | 功能描述:32位微控制器 - MCU ColdFireV1,128KFlash RoHS:否 制造商:Texas Instruments 核心:C28x 處理器系列:TMS320F28x 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:90 MHz 程序存儲(chǔ)器大小:64 KB 數(shù)據(jù) RAM 大小:26 KB 片上 ADC:Yes 工作電源電壓:2.97 V to 3.63 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:LQFP-80 安裝風(fēng)格:SMD/SMT |

| MCF51QM128VHSR | 功能描述:16位微控制器 - MCU ColdFireV1,128KFlash RoHS:否 制造商:Texas Instruments 核心:RISC 處理器系列:MSP430FR572x 數(shù)據(jù)總線寬度:16 bit 最大時(shí)鐘頻率:24 MHz 程序存儲(chǔ)器大小:8 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:2 V to 3.6 V 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:VQFN-40 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。