- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45241 > MC908GR8CDWR2 (FREESCALE SEMICONDUCTOR INC) 8-BIT, FLASH, 8.2 MHz, MICROCONTROLLER, PDSO28 PDF資料下載

參數(shù)資料

| 型號(hào): | MC908GR8CDWR2 |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, FLASH, 8.2 MHz, MICROCONTROLLER, PDSO28 |

| 封裝: | MS-013AE, SOIC-28 |

| 文件頁數(shù): | 128/286頁 |

| 文件大小: | 3708K |

| 代理商: | MC908GR8CDWR2 |

Queuing Transmission Data

MC68HC908GR8 MC68HC908GR4 Data Sheet, Rev. 7

Freescale Semiconductor

213

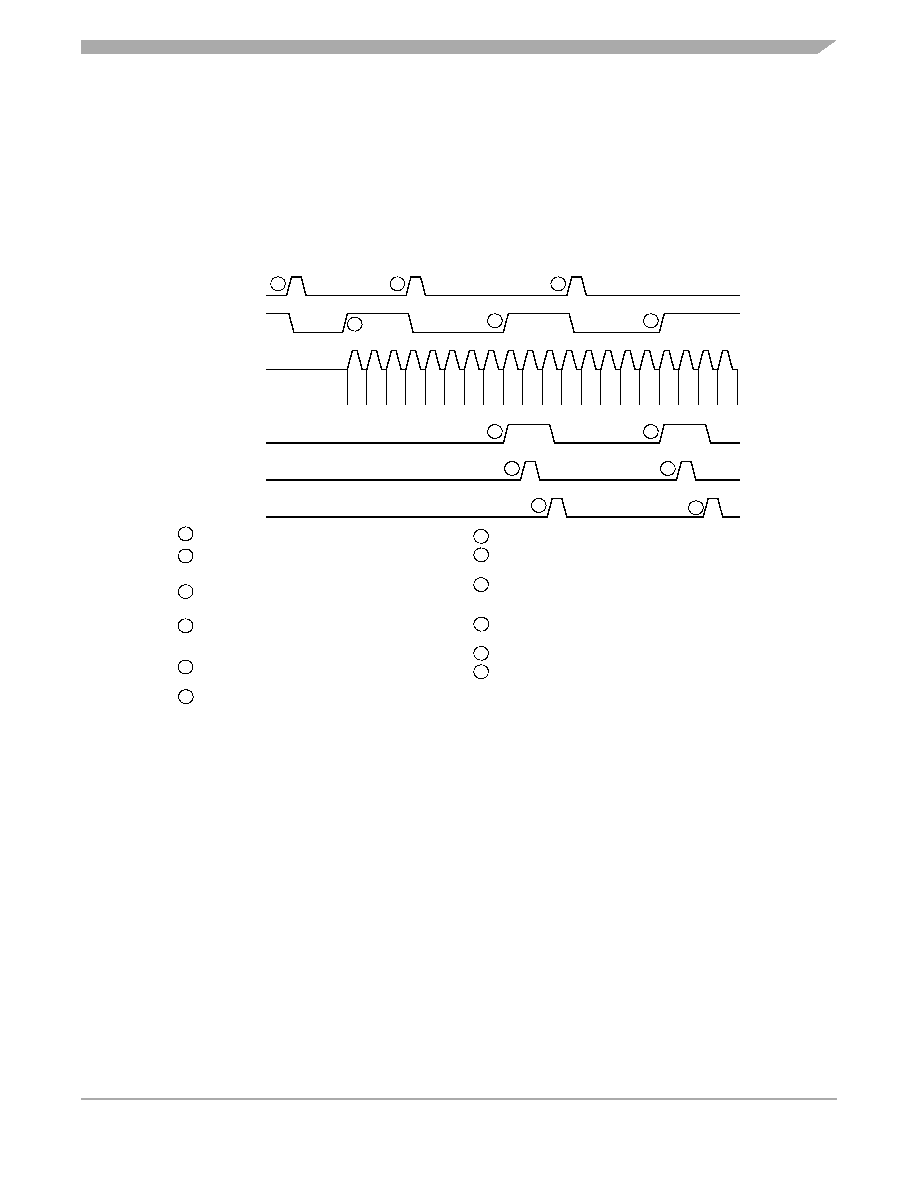

20.6 Queuing Transmission Data

The double-buffered transmit data register allows a data byte to be queued and transmitted. For an SPI

configured as a master, a queued data byte is transmitted immediately after the previous transmission

has completed. The SPI transmitter empty flag (SPTE) indicates when the transmit data buffer is ready

to accept new data. Write to the transmit data register only when the SPTE bit is high. Figure 20-8 shows

the timing associated with doing back-to-back transmissions with the SPI (SPSCK has CPHA: CPOL =

1:0).

Figure 20-8. SPRF/SPTE CPU Interrupt Timing

The transmit data buffer allows back-to-back transmissions without the slave precisely timing its writes

between transmissions as in a system with a single data buffer. Also, if no new data is written to the data

buffer, the last value contained in the shift register is the next data word to be transmitted.

For an idle master or idle slave that has no data loaded into its transmit buffer, the SPTE is set again no

more than two bus cycles after the transmit buffer empties into the shift register. This allows the user to

queue up a 16-bit value to send. For an already active slave, the load of the shift register cannot occur

until the transmission is completed. This implies that a back-to-back write to the transmit data register is

not possible. The SPTE indicates when the next write can occur.

BIT

3

MOSI

SPSCK

SPTE

WRITE TO SPDR

1

CPU WRITES BYTE 2 TO SPDR, QUEUEING BYTE 2

CPU WRITES BYTE 1 TO SPDR, CLEARING SPTE BIT.

BYTE 1 TRANSFERS FROM TRANSMIT DATA

3

1

2

3

5

REGISTER TO SHIFT REGISTER, SETTING SPTE BIT.

SPRF

READ SPSCR

MSB BIT

6

BIT

5

BIT

4

BIT

2

BIT

1

LSB MSB BIT

6

BIT

5

BIT

4

BIT

3

BIT

2

BIT

1

LSB MSB BIT

6

BYTE 2 TRANSFERS FROM TRANSMIT DATA

CPU WRITES BYTE 3 TO SPDR, QUEUEING BYTE

BYTE 3 TRANSFERS FROM TRANSMIT DATA

5

8

10

8

10

4

FIRST INCOMING BYTE TRANSFERS FROM SHIFT

6

CPU READS SPSCR WITH SPRF BIT SET.

4

6

9

SECOND INCOMING BYTE TRANSFERS FROM SHIFT

9

11

AND CLEARING SPTE BIT.

REGISTER TO SHIFT REGISTER, SETTING SPTE BIT.

REGISTER TO RECEIVE DATA REGISTER, SETTING

SPRF BIT.

3 AND CLEARING SPTE BIT.

REGISTER TO SHIFT REGISTER, SETTING SPTE BIT.

REGISTER TO RECEIVE DATA REGISTER, SETTING

SPRF BIT.

12 CPU READS SPDR, CLEARING SPRF BIT.

BIT

5

BIT

4

BYTE 1

BYTE 2

BYTE 3

7

12

READ SPDR

7

CPU READS SPDR, CLEARING SPRF BIT.

11 CPU READS SPSCR WITH SPRF BIT SET.

CPHA:CPOL = 1:0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC908GR4MDWR2 | 8-BIT, FLASH, 8.2 MHz, MICROCONTROLLER, PDSO28 |

| MC68HC908GR4CFA | 8-BIT, FLASH, 8.2 MHz, MICROCONTROLLER, PQFP32 |

| MC68HC908GR8MP | 8-BIT, FLASH, 8.2 MHz, MICROCONTROLLER, PDIP28 |

| MC68HC908GR4CFAE | 8-BIT, FLASH, 8.2 MHz, MICROCONTROLLER, PQFP32 |

| MC68HC908GR4MFA | 8-BIT, FLASH, 8.2 MHz, MICROCONTROLLER, PQFP32 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC908GR8CFAR2 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:Microcontrollers |

| MC908GR8CPE | 功能描述:8位微控制器 -MCU CI 908GR8 EPP RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時(shí)鐘頻率:50 MHz 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| MC908GR8MDWR2 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:Microcontrollers |

| MC908GR8MFAR2 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:M68HC08 Microcontrollers |

| MC908GR8VDWR2 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:Microcontrollers |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。