- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄371076 > MC88PL117FN (MOTOROLA INC) CMOS PLL CLOCK DRIVER PDF資料下載

參數(shù)資料

| 型號(hào): | MC88PL117FN |

| 廠商: | MOTOROLA INC |

| 元件分類: | 時(shí)鐘及定時(shí) |

| 英文描述: | CMOS PLL CLOCK DRIVER |

| 中文描述: | 88PL SERIES, PLL BASED CLOCK DRIVER, 15 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQCC52 |

| 封裝: | PLASTIC, LCC-52 |

| 文件頁(yè)數(shù): | 5/11頁(yè) |

| 文件大小: | 139K |

| 代理商: | MC88PL117FN |

MC88PL117

TIMING SOLUTIONS

BR1333 — Rev 6

5

MOTOROLA

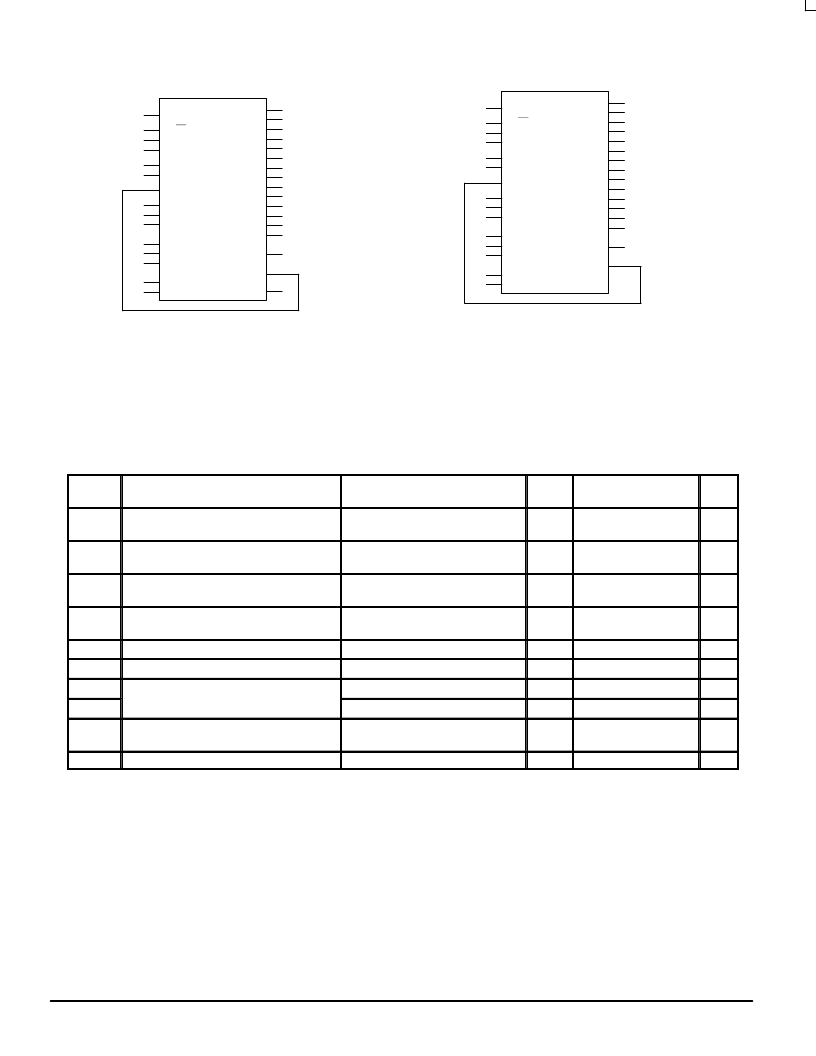

OE/MR

PLL_EN

REF_SEL

OE/MR

PLL_EN

REF_SEL

Q In (80MHz)

2X_Q (120MHz)

2X_Q (120MHz)

Q (60MHz)

Q (60MHz)

Q (60MHz)

Q (60MHz)

Q (60MHz)

Q (60MHz)

Q (60MHz)

Q (60MHz)

Q (60MHz)

Q (60MHz)

Q (60MHz)

Q (60MHz)

0

°

Phase Shift at 60MHz

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

Q8

Q9

Q10

Q11

Q12

Q13

QFEED

LOCK

Q

MC88PL117

FIL

H

H

L

SYNC0

SYNC1

FEEDBACK

OPT2

OPT1

OPT0

H

H

H

L

H

L

MULT1

MULT0

H

H

2

1

0

Q/4 In (16.5MHz)

Q (60MHz)

Q (60MHz)

Q (60MHz)

Q (60MHz)

Q (60MHz)

Q (60MHz)

Q (60MHz)

Q/2 (30MHz)

Q/2 (30MHz)

Q/2 (30MHz)

Q/2 (30MHz)

Q/2 (30MHz)

Q/2 (30MHz)

Q/2 (30MHz)

0

°

Phase Shift at 30MHz

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

Q8

Q9

Q10

Q11

Q12

Q13

QFEED

LOCK

Q

MC88PL117

FIL

H

H

L

SYNC0

SYNC1

FEEDBACK

OPT2

OPT1

OPT0

H

L

L

H

H

H

MULT1

MULT0

L

L

2

1

0

Figure 5. Output Frequency Configuration 5

(OPT0 = L, OPT1 = L, OPT2 = H

Q/4 Input Frequency, MULT0 = L, MULT1 = L)

Figure 6. Output Frequency Configuration 6

(OPT0 = H, OPT1 = H, OPT2 = H

Q Input Frequency, MULT0 = H, MULT1 = H)

DC ELECTRICAL CHARACTERISTICS

(Voltages Referenced to GND) TA =0

°

C to + 70

°

C, VCC = 5.0 V

±

5%

Symbol

Parameter

Test Conditions

VCC

V

Target Limit

Unit

VIH

Minimum High–Level Input

Voltage

Vout = 0.1 V or VCC – 0.1 V

4.75

5.25

2.0

2.0

V

VIL

Maximum Low–Level Input

Voltage

Vout = 0.1 V or VCC – 0.1 V

4.75

5.25

0.8

0.8

V

VOH

Minimum High–Level Output

Voltage

Vin = VIH or VIL

IOH = –36 mA

1

Vin = VIH or VIL

IOL = 36 mA

1

VI = VCC or GND

VI = VCC – 2.1 V

VOLD = 1.0V Max

VOHD = 3.85V Min

VI = VCC or GND

4.75

5.25

4.01

4.51

V

VOL

Maximum Low–Level Output

Voltage

4.75

5.25

0.44

0.44

V

Iin

Maximum Input Leakage Current

5.25

±

1.0

2.0

2

88

μ

A

ICCT

IOLD

IOHD

ICC

Maximum ICC/Input

Minimum Dynamic Output Current

3

5.25

mA

5.25

mA

5.25

–88

mA

Maximum Quiescent Supply

Current (per Package)

5.25

1.0

mA

IOZ

Maximum 3–State Leakage Current

1. IOL and IOH are 12mA and –12mA respectively for the LOCK output.

2. The PLL_EN input pin is not guaranteed to meet this specification.

3. Maximum test duration is 2.0ms, one output loaded at a time.

4. Specification value for IOZ is preliminary, will be finalized upon ‘MC’ status.

VI = VIH or VIL;VO = VCC or GND

5.25

±

50

4

μ

A

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC8T13 | DUAL LINE DRIVERS SILICON MONOLITHIC INTEGRATED CIRCUIT |

| MC8T23 | DUAL LINE DRIVERS SILICON MONOLITHIC INTEGRATED CIRCUIT |

| MC8T14 | TRIPLE LINE RECEIVERS WITH HYSTERESIS |

| MC8T24 | TRIPLE LINE RECEIVERS WITH HYSTERESIS |

| MC8T28 | NONINVERTING BUS TRANSCEIVER MONOLITHIC SCHOTTKY INTEGRATED CIRCUITS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC890P | 制造商:Motorola Inc 功能描述: |

| MC891L | 制造商:Motorola Inc 功能描述: 制造商:MOTOROLA 功能描述: |

| MC891P | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MC893P | 制造商:Motorola Inc 功能描述: |

| MC894P | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Motorola Inc 功能描述: 制造商:MOTOROLA 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。