- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄26807 > MC74HC597ADTR2 (ON SEMICONDUCTOR) HC/UH SERIES, 8-BIT RIGHT PARALLEL IN SERIAL OUT SHIFT REGISTER, TRUE OUTPUT, PDSO16 PDF資料下載

參數(shù)資料

| 型號(hào): | MC74HC597ADTR2 |

| 廠商: | ON SEMICONDUCTOR |

| 元件分類: | 計(jì)數(shù)移位寄存器 |

| 英文描述: | HC/UH SERIES, 8-BIT RIGHT PARALLEL IN SERIAL OUT SHIFT REGISTER, TRUE OUTPUT, PDSO16 |

| 封裝: | PLASTIC, TSSOP-16 |

| 文件頁數(shù): | 7/11頁 |

| 文件大?。?/td> | 291K |

| 代理商: | MC74HC597ADTR2 |

MC54/74HC597A

High–Speed CMOS Logic Data

DL129 — Rev 6

5

MOTOROLA

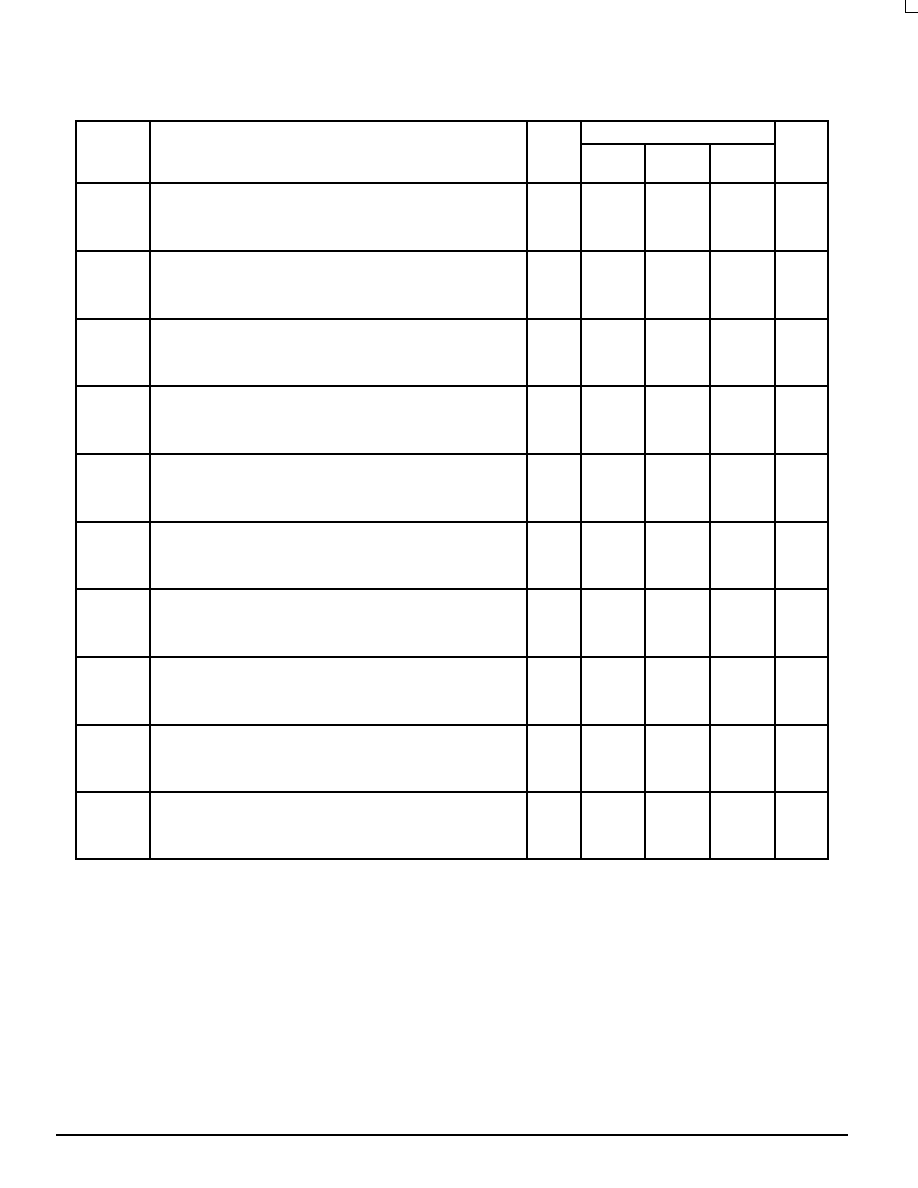

TIMING REQUIREMENTS (Input tr = tf = 6 ns)

Symbol

Parameter

VCC

V

Guaranteed Limit

Unit

Symbol

Parameter

VCC

V

– 55 to

25

_C

v 85_C

v 125_C

Unit

tsu

Minimum Setup Time, Parallel Data inputs A–H to Latch Clock

(Figure 5)

2.0

3.0

4.5

6.0

70

40

15

13

80

45

19

16

90

50

24

20

ns

tsu

Minimum Setup Time, Serial Data Input SA to Shift Clock

(Figure 6)

2.0

3.0

4.5

6.0

70

40

15

13

80

45

19

16

90

50

24

20

ns

tsu

Minimum Setup Time, Serial Shift/Parallel Load to Shift Clock

(Figure 7)

2.0

3.0

4.5

6.0

70

40

15

13

80

45

19

16

90

50

24

20

ns

th

Minimum Hold Time, Latch Clock to Parallel Data Inputs A–H

(Figure 5)

2.0

3.0

4.5

6.0

15

10

2

20

15

3

30

25

5

4

ns

th

Minimum Hold Time, Shift Clock to Serial Data Input SA

(Figure 6)

2.0

3.0

4.5

6.0

2

2

2

ns

trec

Minimum Recovery Time, Reset Inactive to Shift Clock

(Figure 3)

2.0

3.0

4.5

6.0

70

40

15

13

80

45

19

16

90

50

24

20

ns

tw

Minimum Pulse Width, Latch Clock and Shift Clock

(Figures 1 and 2)

2.0

3.0

4.5

6.0

60

35

12

10

70

40

15

13

80

45

19

16

ns

tw

Minimum Pulse Width, Reset

(Figure 3)

2.0

3.0

4.5

6.0

60

35

12

10

70

40

15

13

80

45

19

16

ns

tw

Minimum Pulse Width, Serial Shift/Parallel Load

(Figure 4)

2.0

3.0

4.5

6.0

60

35

12

10

70

40

15

13

80

45

19

16

ns

tr, tf

Maximum Input Rise and Fall Times

(Figure 1)

2.0

3.0

4.5

6.0

1000

800

500

400

1000

800

500

400

1000

800

500

400

ns

NOTE: Information on typical parametric values can be found in Chapter 2 of the Motorola High–Speed CMOS Data Book (DL129/D).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC74HC646DWR2 | HC/UH SERIES, 8-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, PDSO24 |

| MC74HC7266DDR2 | HC/UH SERIES, QUAD 2-INPUT XNOR GATE, PDSO14 |

| MC54HC7266JD | HC/UH SERIES, QUAD 2-INPUT XNOR GATE, CDIP14 |

| MC74HC74AND | HC/UH SERIES, DUAL POSITIVE EDGE TRIGGERED D FLIP-FLOP, COMPLEMENTARY OUTPUT, PDIP14 |

| MC74HC74ADDR2 | HC/UH SERIES, DUAL POSITIVE EDGE TRIGGERED D FLIP-FLOP, COMPLEMENTARY OUTPUT, PDSO14 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC74HC597ADTR2G | 功能描述:計(jì)數(shù)器移位寄存器 IC SHIFT REGISTER 8-BIT RoHS:否 制造商:Texas Instruments 計(jì)數(shù)器類型: 計(jì)數(shù)順序:Serial to Serial/Parallel 電路數(shù)量:1 封裝 / 箱體:SOIC-20 Wide 邏輯系列: 邏輯類型: 輸入線路數(shù)量:1 輸出類型:Open Drain 傳播延遲時(shí)間:650 ns 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 封裝:Reel |

| MC74HC597AF | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MC74HC597D | 制造商:Motorola Inc 功能描述: |

| MC74HC597N | 制造商:Motorola Inc 功能描述: 制造商:Motorola Inc 功能描述:Shift Register, 16 Pin, Plastic, DIP |

| MC74HC640ADT | 制造商:Rochester Electronics LLC 功能描述:- Tape and Reel 制造商:ON Semiconductor 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。