- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371065 > MC74HC4017N (MOTOROLA INC) Decade Counter PDF資料下載

參數(shù)資料

| 型號: | MC74HC4017N |

| 廠商: | MOTOROLA INC |

| 元件分類: | 通用總線功能 |

| 英文描述: | Decade Counter |

| 中文描述: | HC/UH SERIES, SYN POSITIVE EDGE TRIGGERED 10-BIT UP RING COUNTER, PDIP16 |

| 封裝: | PLASTIC, DIP-16 |

| 文件頁數(shù): | 4/9頁 |

| 文件大小: | 224K |

| 代理商: | MC74HC4017N |

MC74HC4017

MOTOROLA

High–Speed CMOS Logic Data

DL129 — Rev 6

4

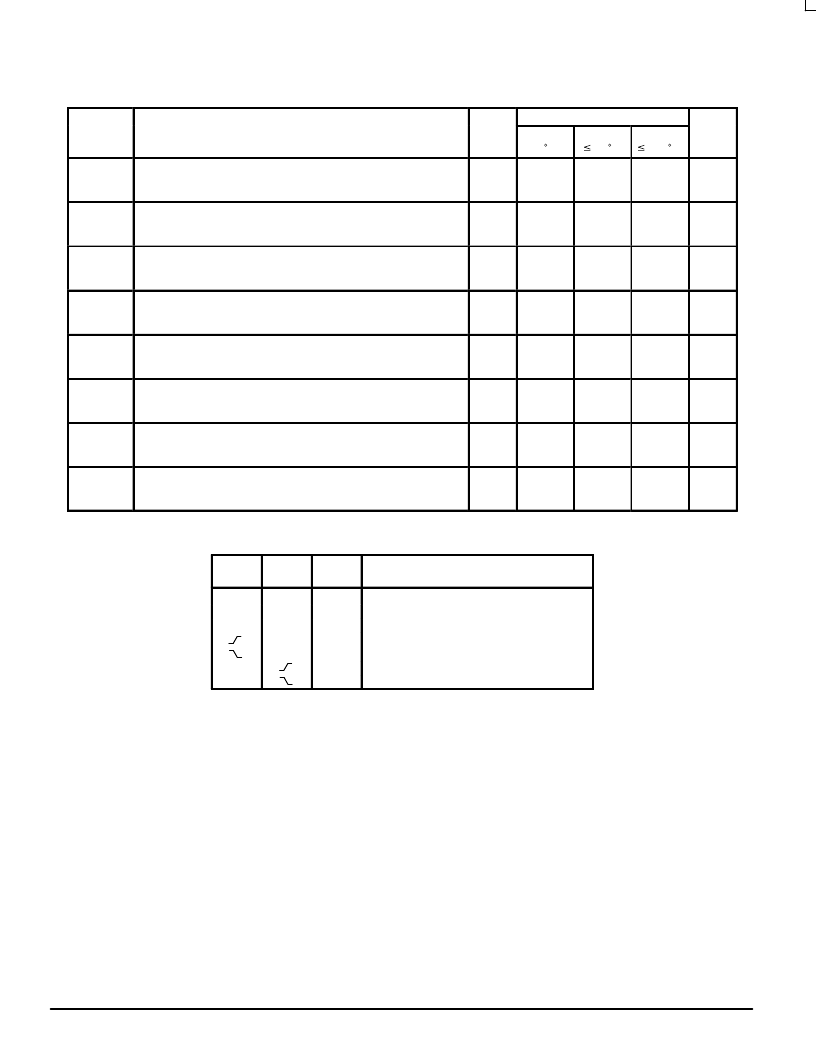

Symbol

tsu

Parameter

V

25 C

85 C

50

50

10

10

20

14

17

80

14

17

80

1000

Unit

ns

Minimum Setup Time, Clock Enable to Clock

2.0

2.0

4.5

4.5

4.5

6.0

2.0

6.0

2.0

2.0

125 C

75

75

15

15

30

20

120

20

120

1000

Minimum Setup Time, Clock Enable to Clock (Inhibit Count)

(Figure 6)

65

ns

(Figure 6)

65

13

(Figure 7)

13

25

tw

Minimum Pulse Width, Reset Input

100

ns

tw

Minimum Pulse Width, Clock Enable Input

100

ns

Maximum Input Rise and Fall Times

1000

ns

FUNCTION TABLE

Clock

Clock

Enable

Reset

Output State*

L

X

X

X

H

X

L

X

L

L

H

L

L

L

L

no change

no change

reset counter, Q0 = H, Q1–Q9 = L, C0 = H

advance to next state

no change

no change

advance to next state

X

H

X = Don’t care

* Carry Out = H for Q0, Q1, Q2, Q3, or Q4 = H; Carry Out = L otherwise.

PIN DESCRIPTIONS

INPUTS

Clock (Pin 14)

Counter clock input. While Clock Enable is low, a low–to–

high transition on this input advances the counter to its next

state.

Reset (Pin 15)

Asynchronous counter reset input. A high level at this input

initializes the counter and forces Q0 and Carry Out to a high,

Q1–Q9 are forced to a low level.

Clock Enable (Pin 13)

Active–low clock enable input. A low level on this input al-

lows the device to count. A high level on this input inhibits the

counting operation. This input may also be used as a

negative–edge clock input. using Clock (Pin 14) as an

active–high enable pin.

OUTPUTS

Q0–Q9 (Pins 3, 2, 4, 7, 10, 1, 5, 6, 9, 11)

Decoded decade counter outputs. Each of these outputs is

high for one clock period only.

Carry Out (Pin 12)

Cascading output pin. This output is used either as a cas-

cading output or a symmetrical divide–by–ten output. This

output goes low when a count of five is reached and high

when the counter advances to zero or when reset. When the

counters are cascaded this output provides a rising–edge

signal for the clock input of the next counter stage.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC74HC4020AD | 14-Stage Binary Ripple Counter |

| MC74HC4020ADT | 14-Stage Binary Ripple Counter |

| MC74HC4020AN | 14-Stage Binary Ripple Counter |

| MC74HC4024D | 7-Stage Binary Ripple Counter |

| MC74HC4024N | 7-Stage Binary Ripple Counter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC74HC4020AD | 功能描述:計數(shù)器移位寄存器 2-6V Monolithic WFR RoHS:否 制造商:Texas Instruments 計數(shù)器類型: 計數(shù)順序:Serial to Serial/Parallel 電路數(shù)量:1 封裝 / 箱體:SOIC-20 Wide 邏輯系列: 邏輯類型: 輸入線路數(shù)量:1 輸出類型:Open Drain 傳播延遲時間:650 ns 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 封裝:Reel |

| MC74HC4020ADG | 功能描述:計數(shù)器移位寄存器 2-6V Monolithic WFR Binary RoHS:否 制造商:Texas Instruments 計數(shù)器類型: 計數(shù)順序:Serial to Serial/Parallel 電路數(shù)量:1 封裝 / 箱體:SOIC-20 Wide 邏輯系列: 邏輯類型: 輸入線路數(shù)量:1 輸出類型:Open Drain 傳播延遲時間:650 ns 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 封裝:Reel |

| MC74HC4020ADR2 | 功能描述:計數(shù)器移位寄存器 2-6V Monolithic WFR RoHS:否 制造商:Texas Instruments 計數(shù)器類型: 計數(shù)順序:Serial to Serial/Parallel 電路數(shù)量:1 封裝 / 箱體:SOIC-20 Wide 邏輯系列: 邏輯類型: 輸入線路數(shù)量:1 輸出類型:Open Drain 傳播延遲時間:650 ns 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 封裝:Reel |

| MC74HC4020ADR2G | 功能描述:計數(shù)器移位寄存器 2-6V Monolithic WFR Binary RoHS:否 制造商:Texas Instruments 計數(shù)器類型: 計數(shù)順序:Serial to Serial/Parallel 電路數(shù)量:1 封裝 / 箱體:SOIC-20 Wide 邏輯系列: 邏輯類型: 輸入線路數(shù)量:1 輸出類型:Open Drain 傳播延遲時間:650 ns 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 封裝:Reel |

| MC74HC4020ADT | 制造商:ON Semiconductor 功能描述:Counter Single 14-Bit Binary UP 16-Pin TSSOP Rail 制造商:Rochester Electronics LLC 功能描述:- Tape and Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復。