- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45226 > MC68HC11A1MFU2 (ABILIS SYSTEMS) 8-BIT, MROM, 2 MHz, MICROCONTROLLER, PQFP64 PDF資料下載

參數(shù)資料

| 型號: | MC68HC11A1MFU2 |

| 廠商: | ABILIS SYSTEMS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 2 MHz, MICROCONTROLLER, PQFP64 |

| 封裝: | QFP-64 |

| 文件頁數(shù): | 22/158頁 |

| 文件大小: | 3803K |

| 代理商: | MC68HC11A1MFU2 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當(dāng)前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁

CPU, ADDRESSING MODES, AND INSTRUCTION SET

MC68HC11A8

10-20

TECHNICAL DATA

10

6-7

LDY

6

1

2

3

4

5

6

Opcode Address

Opcode Address + 1

Opcode Address + 2

$FFFF

(IX) + Offset

(IX) + Offset + 1

1

Opcode (Page Select Byte)

($1A)

Opcode (Second Byte) ($EE)

Index Offset

Irrelevant Data

Operand Data (High Byte)

Operand Data (Low Byte)

6-8

STD, STS, STX

5

1

2

3

4

5

Opcode Address

Opcode Address + 1

$FFFF

(IX) + Offset

(IX) + Offset + 1

1

0

Opcode

Index Offset

Irrelevant Data

Register Data (High Byte)

Register Data (Low Byte)

6-9

STY

6

1

2

3

4

5

6

Opcode Address

Opcode Address + 1

Opcode Address + 2

$FFFF

(IX) + Offset

(IX) + Offset + 1

1

0

Opcode (Page Select Byte)

($1A)

Opcode (Second Byte) ($EF)

Index Offset

Irrelevant Data

Register Data (High Byte)

Register Data (Low Byte)

6-10

ADDD, CPX, SUBD

6

1

2

3

4

5

6

Opcode Address

Opcode Address + 1

$FFFF

(IX) + Offset

(IX) + Offset + 1

$FFFF

1

Opcode

Index Offset

Irrelevant Data

Operand Data (High Byte)

Operand Data (Low Byte)

Irrelevant Data

6-11

CPD, CPY

7

1

2

3

4

5

6

7

Opcode Address

Opcode Address + 1

Opcode Address + 2

$FFFF

(IX) + Offset

(IX) + Offset + 1

$FFFF

1

Opcode (Page Select Byte)

Opcode (Second Byte)

Index Offset

Irrelevant Data

Operand Data (High Byte)

Operand Data (Low Byte)

Irrelevant Data

6-12

JSR

6

1

2

3

4

5

6

Opcode Address

Opcode Address + 1

$FFFF

(IX) + Offset

Stack Pointer

Stack Pointer – 1

1

0

Opcode ($AD)

Index Offset

Irrelevant Data

First Opcode in Subroutine

Return Address (Low Byte)

Return Address (High Byte)

6-13

BCLR, BSET

7

1

2

3

4

5

6

7

Opcode Address

Opcode Address + 1

$FFFF

(IX) + Offset

Opcode Address + 2

$FFFF

(IX) + Offset

1

0

Opcode

Index Offset

Irrelevant Data

Original Operand Data

Mask Byte

Irrelevant Data

Result Operand Data

6-14

BRCLR, BRSET

7

1

2

3

4

5

6

7

Opcode Address

Opcode Address + 1

$FFFF

(IX) + Offset

Opcode Address + 2

Opcode Address + 3

$FFFF

1

Opcode

Index Offset

Irrelevant Data

Original Operand Data

Mask Byte

Branch Offset

Irrelevant Data

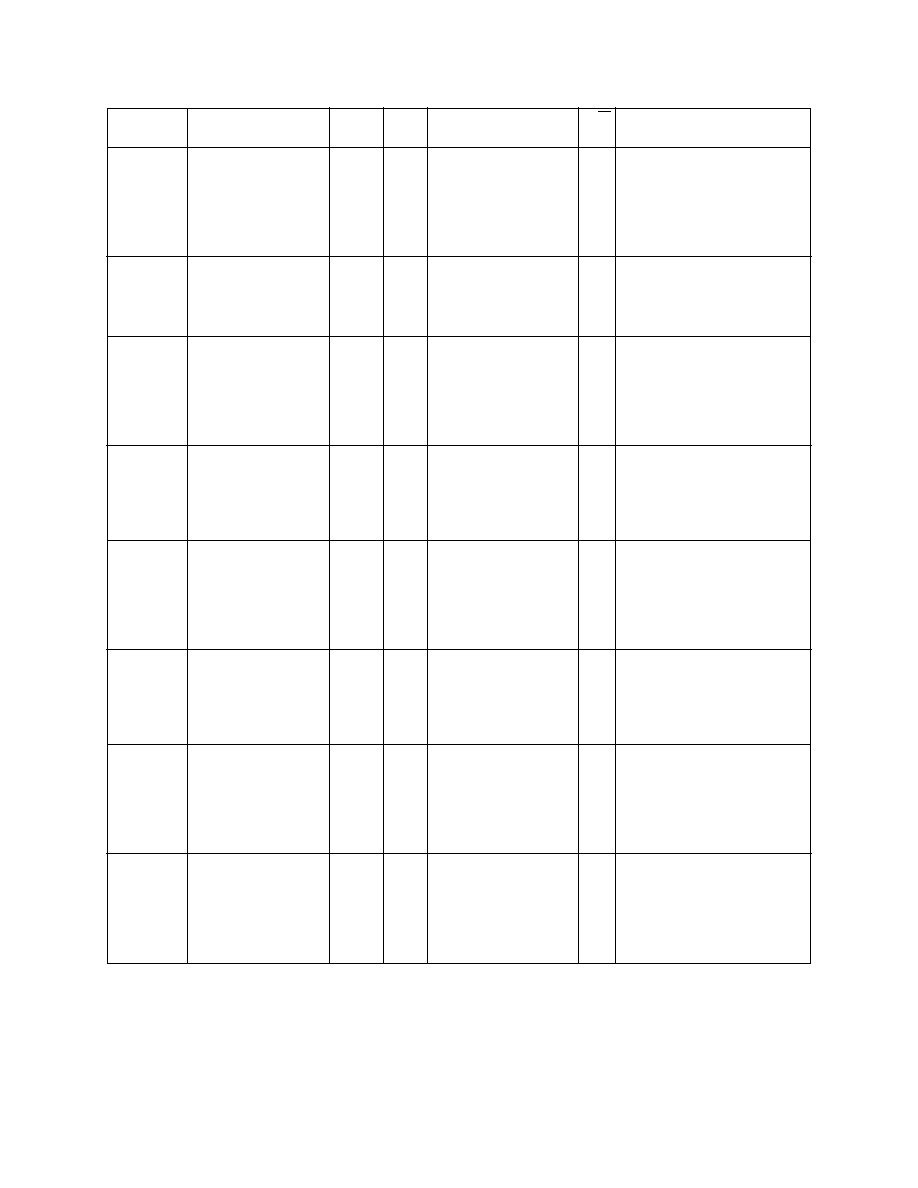

Table 10-6 Cycle-by-Cycle Operation — Indexed X Mode (Sheet 2 of 2)

Reference

Number*

Address Mode

and Instructions

Cycles Cycle

#

Address Bus

R/W

Line

Data Bus

*The reference number is given to provide a cross-reference to Table 10-1.

F

re

e

sc

a

le

S

e

m

ic

o

n

d

u

c

to

r,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

c

..

.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC68HC11A8BMP2 | 8-BIT, MROM, 2 MHz, MICROCONTROLLER, PDIP48 |

| MC68HCP11A1VP2 | 8-BIT, MROM, 2 MHz, MICROCONTROLLER, PDIP48 |

| MC68HC11A8P1 | 8-BIT, MROM, MICROCONTROLLER, PDIP48 |

| MC68HC11A1MP | 8-BIT, EEPROM, 2 MHz, MICROCONTROLLER, PDIP48 |

| MC68HC11A8VFN1 | 8-BIT, MROM, 3 MHz, MICROCONTROLLER, PQCC52 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC68HC11A1MP | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:8-Bit Microcontrollers |

| MC68HC11A1MP2 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:HCMOS Single-Chip Microcontroller |

| MC68HC11A1P | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:8-Bit Microcontrollers |

| MC68HC11A1VFN | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:8-Bit Microcontrollers |

| MC68HC11A1VFN2 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:HCMOS Single-Chip Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。