- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382301 > MC33121FN (MOTOROLA INC) LOW VOLTAGE SUBSCRIBER LOOP INTERFACE CIRCUIT PDF資料下載

參數(shù)資料

| 型號(hào): | MC33121FN |

| 廠商: | MOTOROLA INC |

| 元件分類: | 模擬傳輸電路 |

| 英文描述: | LOW VOLTAGE SUBSCRIBER LOOP INTERFACE CIRCUIT |

| 中文描述: | TELECOM-SLIC, PQCC28 |

| 封裝: | PLASTIC, LCC-28 |

| 文件頁數(shù): | 23/32頁 |

| 文件大小: | 570K |

| 代理商: | MC33121FN |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁當(dāng)前第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

MC33121

MOTOROLA

23

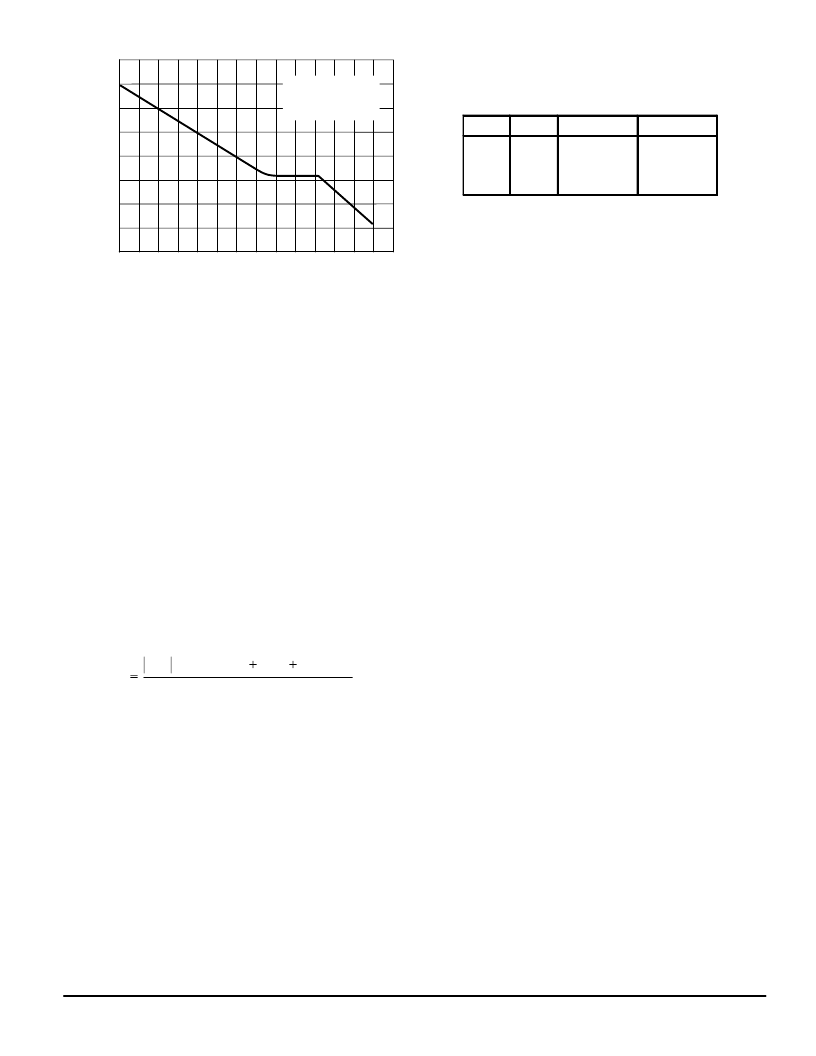

Figure 39. Thermal Resistance

(Junction–to–Ambient)

70

25

60

50

30

TA,

°

C

MC33121

STILL AIR, SOLDERED

TO A G–10 PC BOARD

40

35

45

55

65

75

85

θ

C

°

,

Selecting the Transistors

The specifications for the two loop current pass transistors

involve their current gain, voltage rating, and power dissipa-

tion capabilities at the highest ambient temperatures. Power

dissipation during both normal operation and faults must be

considered when determining worst case situations. Gener-

ally, more power is dissipated during a fault condition than

during normal operation.

The transistors’ minimum beta is recommended to be 40 at

the loop currents involved in the application. A lower beta

could degrade gain and balance performance. Maximum

beta should be less than 500 to prevent possible oscillations.

Darlington type transistors should not be used. The voltage

rating should be consistent with the maximum VEE, expected

transients, and the protection scheme used.

Referring to Figure 27, during normal operation the loop

current and the voltage across the transistors are both at a

maximum when the load impedance (RL) is at a minimum.

The loop current is determined by RRF and the graphs of

Figures 5 – 7. The voltage across each transistor is deter-

mined from the following:

VT

VEE– 2.1 – [(65

2RP

RL)

IL]

2

(22)

The power in each transistor is then (VT

IL). The voltage

across the two transistors will always be nearly equal during

normal operation, resulting in equal power dissipation. The

graph of Figure 24 indicates the power dissipated in each

transistor where RP = 100

.

During a fault condition, depicted in Figure 38, if the leak-

age resistance from Tip to VEE or from Ring to VCC is less

than that shown in Figures 12 – 14 (when off–hook), the

MC33121 will power down the transistors to protect them

from overheating. Should the leakage resistance be slightly

higher than that shown in the graphs, however, and the fault

detection has not been activated, the power in one transistor

(in a single fault, both transistors in a double fault) will be

higher than normal. The power will depend on VEE, RL, RP

and the leakage resistance. Table 3 is a guide of the power in

the transistor dissipating the higher power level.

The power (in watts) in the two right columns indicates the

power dissipated by that transistor if it is carrying the maxi-

mum fault current. The system designer should attempt to

predict possible fault conditions for the system, and then

measure the conditions on the transistors during the worse

case fault(s).

Table 3. Transistor Power During a Fault

VEE

– 42

– 24

– 42

– 24

RL

PPNP

0.835

0.257

0.601

0.109

PNPN

0.615

0.176

0.185

0.057

150

150

600

600

For most applications involving a maximum loop current of

30 – 40 mA, and a maximum TA of + 85

°

C, and where faults

may occur, the MJD243 and MJD253 DPAK transistors are

recommended. When mounted as described in their data

sheet, they will handle both the normal loop current as well

as most fault conditions. If faults are not expected to occur in

a particular application, then smaller package transistors,

such as MPS6717 and MPS6729, may be used. Each ap-

plication must be evaluated individually when selecting the

transistors.

Other possible transistors which can be considered:

PNP

NPN

MJD253–1

MJE253

MJD32

MJD42

MJD350

TIP30A,B,C

MJD243–1

MJE243

MJD31

MJD41

MJD340

TIP29A,B,C

Longitudinal Current Capability

The maximum longitudinal current which can be handled

without distortion is a function of loop current, battery feed re-

sistance, the longitudinal impedance, and the components

on ST2.

Since the pass transistors cannot pass current in the re-

verse direction, the DC loop current provides one upper

boundary for the peak longitudinal current plus peak speech

signal current. The battery feed resistance determines, in ef-

fect, the DC voltage across the transistors, which is a mea-

sure of the headroom available for the circuit to handle the

peak longitudinal voltage plus peak speech signal voltage.

The longitudinal impedance, determined by the RS resistors

(equation 4), determines the longitudinal current for a given

longitudinal voltage.

While analysis of the above items may yield one value of

maximum longitudinal current, a different limit (which may

be higher or lower) is imposed by the capacitor CT, and any

pulldown resistance RT, on Pin 12 (ST2). This is due to the

fact that the sense currents at TSI and RSI will be alternately

mismatched as Tip and Ring move up and down together in

the presence of longitudinal signals. When the longitudinals

are strong, the internal fault detect circuit is activated with

each 1/2 cycle, which attempts to switch ST2 low (see the

section on Fault Detection). The speed at which ST2 can

switch low is a function of both the external capacitor, CT and

any pulldown resistance, RT.

The graphs of Figures 25 and 26 indicate the maximum

longitudinal current which can be handled (in Tip and in Ring)

without distortion or causing ST2 to switch low.

PC Board Layout Considerations

PC board considerations include thermal, RFI/EMI, tran-

sient conditions, interconnection of the four wire side to the

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC33121P | LOW VOLTAGE SUBSCRIBER LOOP INTERFACE CIRCUIT |

| MC33151 | High Speed Dual MOSFET Drivers |

| MC33151DR2 | High Speed Dual MOSFET Drivers |

| MC34151DR2 | High Speed Dual MOSFET Drivers |

| MC33151VDR2 | 0.022 UF 10% 50V X7R (0603) CAP TR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC33121P | 制造商:Rochester Electronics LLC 功能描述:SLIC III - Bulk |

| MC33128 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:POWER MANAGEMENT CONTROLLER |

| MC33128D | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:POWER MANAGEMENT CONTROLLER |

| MC33129 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:High Performance Current Mode Controllers |

| MC33129D | 制造商:Motorola Inc 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。