- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382294 > MC14073BDG (ON SEMICONDUCTOR) Replaced by TPS2377 : Legacy/IEEE802.3af Compatible Power Interface Switch for PoE PDs 8-TSSOP 0 to 70 PDF資料下載

參數(shù)資料

| 型號: | MC14073BDG |

| 廠商: | ON SEMICONDUCTOR |

| 元件分類: | 通用總線功能 |

| 英文描述: | Replaced by TPS2377 : Legacy/IEEE802.3af Compatible Power Interface Switch for PoE PDs 8-TSSOP 0 to 70 |

| 中文描述: | 4000/14000/40000 SERIES, TRIPLE 3-INPUT AND GATE, PDSO14 |

| 封裝: | LEAD FREE, SOIC-14 |

| 文件頁數(shù): | 9/11頁 |

| 文件大小: | 327K |

| 代理商: | MC14073BDG |

MOTOROLA CMOS LOGIC DATA

15

MC14001B

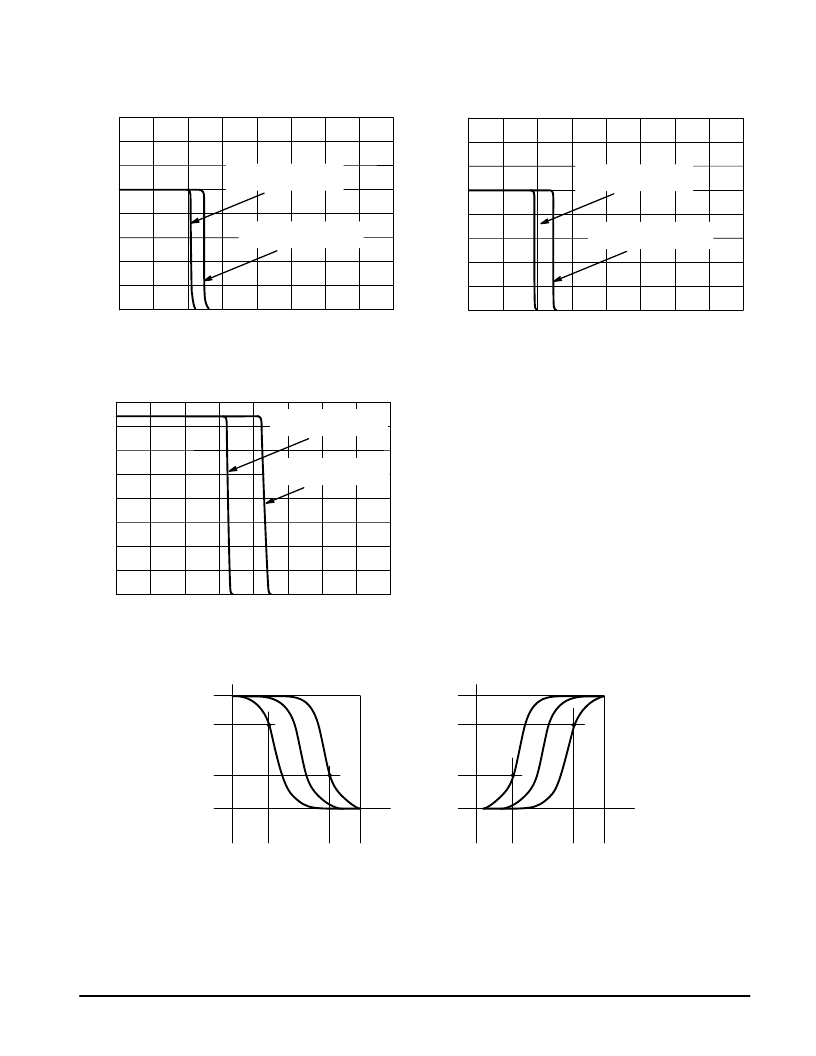

TYPICAL B–SERIES GATE CHARACTERISTICS (cont’d)

VOLTAGE TRANSFER CHARACTERISTICS

Figure 8. VDD = 5.0 Vdc

Figure 9. VDD = 10 Vdc

1.0

3.0

5.0

4.0

2.0

0

1.0

3.0

5.0

4.0

2.0

0

0

0

Vin, INPUT VOLTAGE (Vdc)

SINGLE INPUT NAND, AND

MULTIPLE INPUT NOR, OR

SINGLE INPUT NOR, OR

MULTIPLE INPUT NAND, AND

SINGLE INPUT NAND, AND

MULTIPLE INPUT NOR, OR

SINGLE INPUT NOR, OR

MULTIPLE INPUT NAND, AND

2.0

6.0

10

8.0

4.0

2.0

6.0

10

8.0

4.0

Vin, INPUT VOLTAGE (Vdc)

V

o

V

o

Figure 10. VDD = 15 Vdc

0

0

SINGLE INPUT NAND, AND

MULTIPLE INPUT NOR, OR

SINGLE INPUT NOR, OR

MULTIPLE INPUT NAND, AND

2.0

6.0

10

8.0

4.0

2.0

6.0

10

8.0

4.0

Vin, INPUT VOLTAGE (Vdc)

12

14

16

V

o

DC NOISE MARGIN

The DC noise margin is defined as the input voltage range

from an ideal “1” or “0” input level which does not produce

output state change(s). The typical and guaranteed limit val-

ues of the input values VIL and VIH for the output(s) to be at a

fixed voltage VO are given in the Electrical Characteristics

table. VIL and VIH are presented graphically in Figure 11.

Guaranteed minimum noise margins for both the “1” and

“0” levels =

1.0 V with a 5.0 V supply

2.0 V with a 10.0 V supply

2.5 V with a 15.0 V supply

Figure 11. DC Noise Immunity

Vout

VO

VO

VIL

0

VIH

Vin

VDD

VDD

Vout

VO

VO

VIL

0

VIH

Vin

VDD

VDD

(a) Inverting Function

(b) Non–Inverting Function

VSS = 0 VOLTS DC

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC14073BDR2 | Replaced by TPS2377 : Legacy/IEEE802.3af Compatible Power Interface Switch for PoE PDs 8-TSSOP 0 to 70 |

| MC14073BDR2G | B-SUFFIX SERIES CMOS GATES |

| MC14073BFEL | B-SUFFIX SERIES CMOS GATES |

| MC14011BCP | B-SUFFIX SERIES CMOS GATES |

| MC14011BD | 1A Single-Slot PC Card Power Switch w/ Parallel Interface 20-HTSSOP -40 to 85 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC14073BDR2 | 功能描述:邏輯門 3-18V Triple 3-Input RoHS:否 制造商:Texas Instruments 產(chǎn)品:OR 邏輯系列:LVC 柵極數(shù)量:2 線路數(shù)量(輸入/輸出):2 / 1 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 傳播延遲時間:3.8 ns 電源電壓-最大:5.5 V 電源電壓-最小:1.65 V 最大工作溫度:+ 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DCU-8 封裝:Reel |

| MC14073BDR2G | 功能描述:邏輯門 3-18V Triple 3-Input AND RoHS:否 制造商:Texas Instruments 產(chǎn)品:OR 邏輯系列:LVC 柵極數(shù)量:2 線路數(shù)量(輸入/輸出):2 / 1 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 傳播延遲時間:3.8 ns 電源電壓-最大:5.5 V 電源電壓-最小:1.65 V 最大工作溫度:+ 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DCU-8 封裝:Reel |

| MC14073BFEL | 功能描述:邏輯門 3-18V Triple 3-Input RoHS:否 制造商:Texas Instruments 產(chǎn)品:OR 邏輯系列:LVC 柵極數(shù)量:2 線路數(shù)量(輸入/輸出):2 / 1 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 傳播延遲時間:3.8 ns 電源電壓-最大:5.5 V 電源電壓-最小:1.65 V 最大工作溫度:+ 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DCU-8 封裝:Reel |

| MC14073BFELG | 功能描述:邏輯門 3-18V Triple 3-Input AND RoHS:否 制造商:Texas Instruments 產(chǎn)品:OR 邏輯系列:LVC 柵極數(shù)量:2 線路數(shù)量(輸入/輸出):2 / 1 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 傳播延遲時間:3.8 ns 電源電壓-最大:5.5 V 電源電壓-最小:1.65 V 最大工作溫度:+ 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DCU-8 封裝:Reel |

| MC14075B | 制造商:Motorola Inc 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。