- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384719 > MC100EP446MNR4G (ON SEMICONDUCTOR) 3.3 V/5 V 8-Bit CMOS/ECL/TTL Data Input Parallel/Serial Converter PDF資料下載

參數(shù)資料

| 型號: | MC100EP446MNR4G |

| 廠商: | ON SEMICONDUCTOR |

| 元件分類: | 通用總線功能 |

| 英文描述: | 3.3 V/5 V 8-Bit CMOS/ECL/TTL Data Input Parallel/Serial Converter |

| 中文描述: | 100E SERIES, 8-BIT RIGHT PARALLEL IN SERIAL OUT SHIFT REGISTER, COMPLEMENTARY OUTPUT, PQCC32 |

| 封裝: | 5 X 5 MM, 1 MM HEIGHT, 0.50 MM PITCH, LEAD FREE, QFN-32 |

| 文件頁數(shù): | 16/20頁 |

| 文件大?。?/td> | 278K |

| 代理商: | MC100EP446MNR4G |

MC10EP446, MC100EP446

http://onsemi.com

16

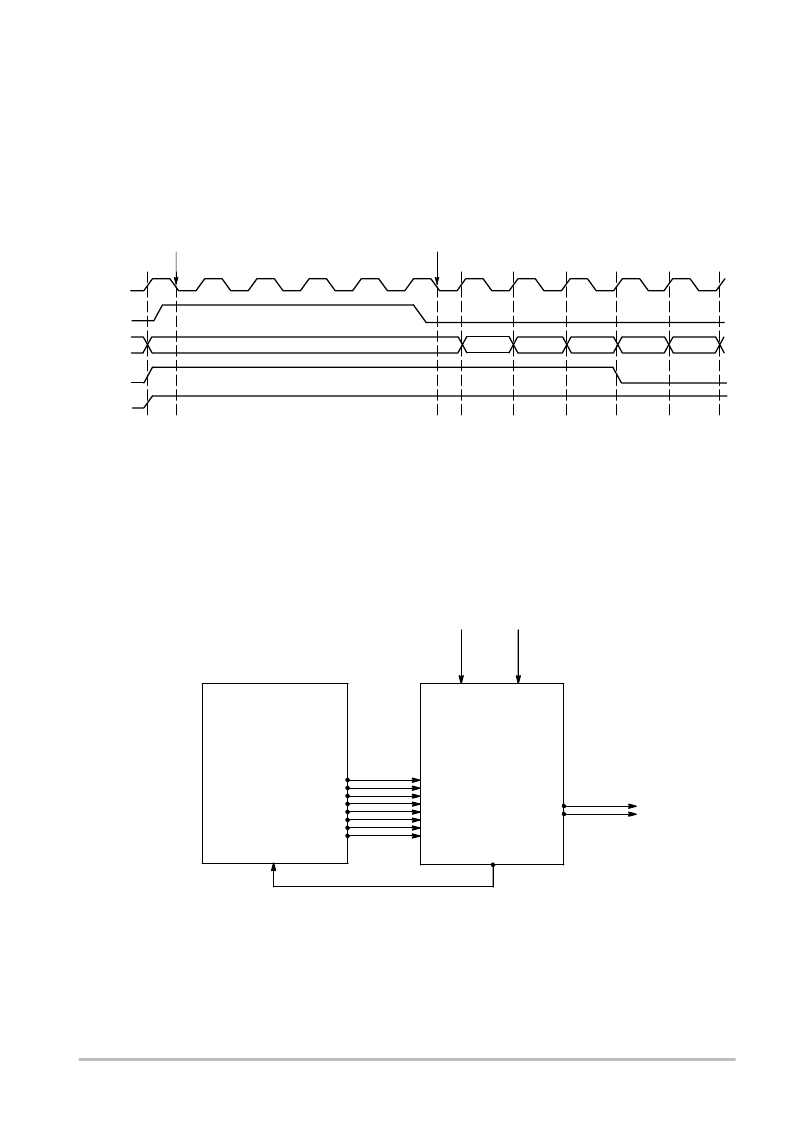

The differential synchronous CKEN inputs (Pins 6 and 7), disable the internal clock circuitry. The synchronous CKEN will

suspend all of the device activities and prevent runt pulses from being generated. The rising edge of CKEN followed by the

falling edge of CLK will suspend all activities. The falling edge of CKEN followed by the falling edge of CLK will resume

all activities (Figure 13).

Figure 13. Timing Diagram with CKEN with CKSEL HIGH

CLK

CKEN

SOUT

CKSEL

D1

1

D0

1

D2

1

D3

1

PCLK

D4

1

D5

1

Internal Clock

Disabled

Internal Clock

Enabled

The differential PCLK output (Pins 14 and 15) is a word

framer and can help the user synchronize the serial data

output, S

OUT

(Pins 11 and 12), in their applications.

Furthermore, PCLK can be used as a trigger for input

parallel data (Figure 14).

An internally generated voltage supply, the V

BB

pin, is

available to this device only. For single–ended input

conditions, the unused differential input is connected to V

BB

as a switching reference voltage. V

BB

may also rebias AC

coupled inputs. When used, decouple V

BB

and V

CC

via a

0.01 F capacitor and limit current sourcing or sinking to

0.5 mA. When not used, V

BB

should be left open. Also, both

outputs of the differential pair must be terminated (50 to

V

TT

) even if only one output is used.

Figure 14. PCLK as Trigger Application

TRIGGER

Pattern Generator

Data Format Logic

(FPGA, ASIC)

P

D

CLK

PCLK

EP446

P

D

SYNC

S

OUT

SERIAL DATA

CLK

RESET

相關PDF資料 |

PDF描述 |

|---|---|

| MC10EP446FAG | 3.3 V/5 V 8-Bit CMOS/ECL/TTL Data Input Parallel/Serial Converter |

| MC10EP446FAR2G | 3.3 V/5 V 8-Bit CMOS/ECL/TTL Data Input Parallel/Serial Converter |

| MC10EP446MNG | 3.3 V/5 V 8-Bit CMOS/ECL/TTL Data Input Parallel/Serial Converter |

| MC10EP446MNR4G | 3.3 V/5 V 8-Bit CMOS/ECL/TTL Data Input Parallel/Serial Converter |

| MC100EP446FAG | 3.3 V/5 V 8-Bit CMOS/ECL/TTL Data Input Parallel/Serial Converter |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MC100EP451 | 制造商:ONSEMI 制造商全稱:ON Semiconductor 功能描述:3.3V / 5VECL 6-Bit Differential Register with Master Reset |

| MC100EP451FA | 功能描述:觸發(fā)器 3.3V/5V ECL 6-Bit RoHS:否 制造商:Texas Instruments 電路數(shù)量:2 邏輯系列:SN74 邏輯類型:D-Type Flip-Flop 極性:Inverting, Non-Inverting 輸入類型:CMOS 輸出類型: 傳播延遲時間:4.4 ns 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:X2SON-8 封裝:Reel |

| MC100EP451FAG | 功能描述:觸發(fā)器 3.3V/5V ECL 6-Bit Diff w/Master Reset RoHS:否 制造商:Texas Instruments 電路數(shù)量:2 邏輯系列:SN74 邏輯類型:D-Type Flip-Flop 極性:Inverting, Non-Inverting 輸入類型:CMOS 輸出類型: 傳播延遲時間:4.4 ns 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:X2SON-8 封裝:Reel |

| MC100EP451FAR2 | 功能描述:觸發(fā)器 3.3V/5V ECL 6-Bit RoHS:否 制造商:Texas Instruments 電路數(shù)量:2 邏輯系列:SN74 邏輯類型:D-Type Flip-Flop 極性:Inverting, Non-Inverting 輸入類型:CMOS 輸出類型: 傳播延遲時間:4.4 ns 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:X2SON-8 封裝:Reel |

| MC100EP451FAR2G | 功能描述:觸發(fā)器 3.3V/5V ECL 6-Bit Diff w/Master Reset RoHS:否 制造商:Texas Instruments 電路數(shù)量:2 邏輯系列:SN74 邏輯類型:D-Type Flip-Flop 極性:Inverting, Non-Inverting 輸入類型:CMOS 輸出類型: 傳播延遲時間:4.4 ns 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:X2SON-8 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復。