- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45201 > MB9AF112NPF RISC MICROCONTROLLER, PQFP100 PDF資料下載

參數(shù)資料

| 型號: | MB9AF112NPF |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | RISC MICROCONTROLLER, PQFP100 |

| 封裝: | 0.65 MM PITCH, PLASTIC, LQFP-100 |

| 文件頁數(shù): | 83/112頁 |

| 文件大?。?/td> | 1225K |

| 代理商: | MB9AF112NPF |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁當前第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁

72

FUJITSU SEMICONDUCTOR CONFIDENTIAL

r2.1

MB9A110 Series

DS706-00011-1v0-E

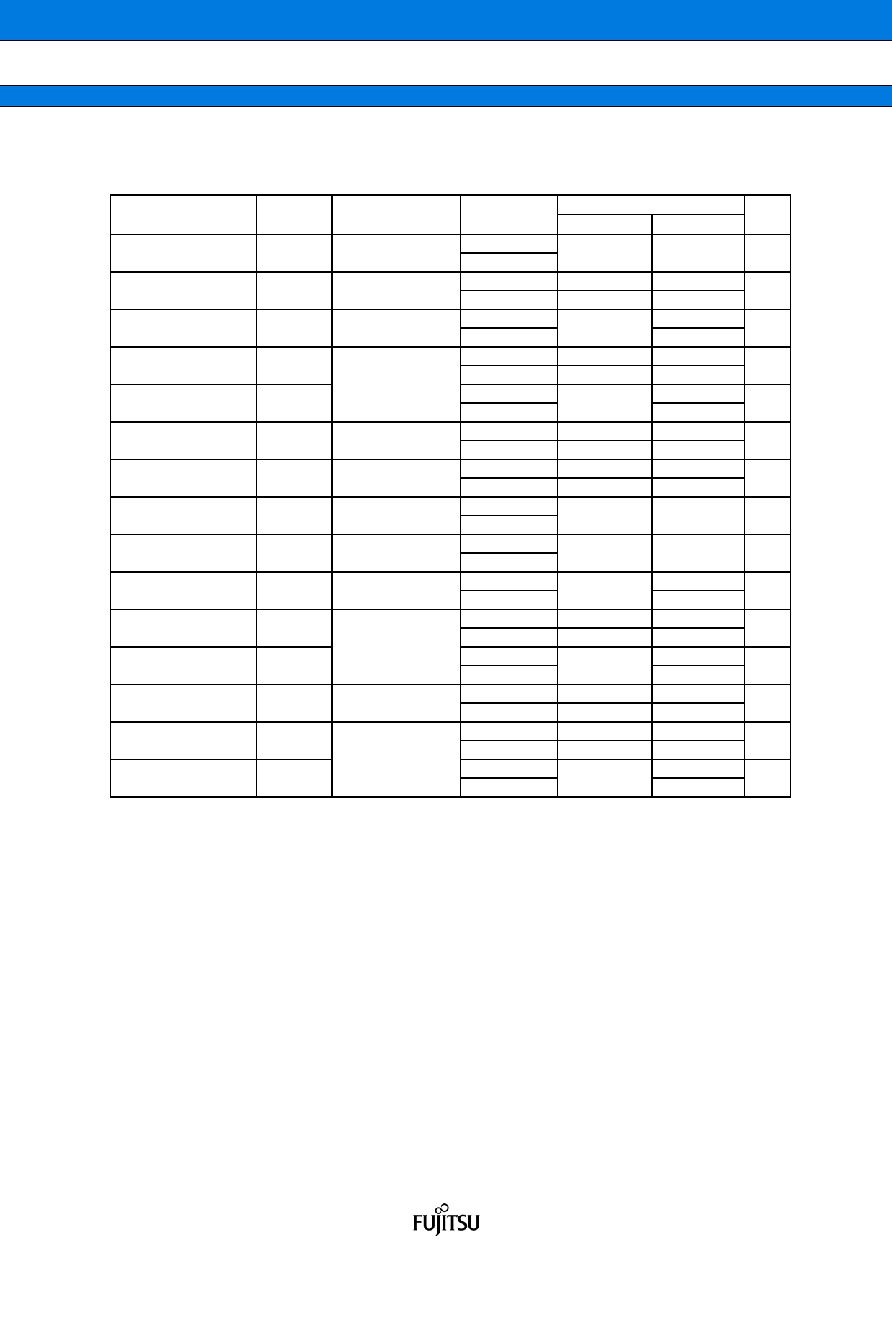

Separate Bus Access Asynchronous SRAM Mode

(Vcc = 2.7V to 5.5V, Vss = 0V, Ta = - 40°C to + 105°C)

Value

Parameter

Symbol

Pin name

Conditions

Min

Max

Unit

Vcc ≥ 4.5V

MOEX

Min pulse width

tOEW

MOEX

Vcc < 4.5V

MCLK×n-3

-

ns

Vcc ≥ 4.5V

-9

9

MCSX ↓ → Address

output delay time

tCSL – AV

MCSX[7:0]

MAD[24:0]

Vcc < 4.5V

-12

12

ns

Vcc ≥ 4.5V

MCLK×m+9

MOEX ↑ →

Address hold time

tOEH - AX

MOEX

MAD[24:0]

Vcc < 4.5V

0

MCLK×m+12

ns

Vcc ≥ 4.5V

MCLK×m-9 MCLK×m+9

MCSX ↓ →

MOEX ↓ delay time

tCSL - OEL

Vcc < 4.5V

MCLK×m-12 MCLK×m+12

ns

Vcc ≥ 4.5V

MCLK×m+9

MOEX ↑ →

MCSX ↑ time

tOEH - OSH

MOEX

MCSX[7:0]

Vcc < 4.5V

0

MCLK×m+12

ns

Vcc ≥ 4.5V

MCLK×m-9 MCLK×m+9

MCSX ↓ →

MDQM ↓ delay time

tCSL - RDQML

MOEX

MDQM[1:0]

Vcc < 4.5V

MCLK×m-12 MCLK×m+12

ns

Vcc ≥ 4.5V

20

-

Data set up →

MOEX ↑ time

tDS - OE

MOEX

MADATA[15:0]

Vcc < 4.5V

38

-

ns

Vcc ≥ 4.5V

MOEX ↑ →

Data hold time

tDH - OE

MOEX

MADATA[15:0]

Vcc < 4.5V

0

-

ns

Vcc ≥ 4.5V

MWEX

Min pulse width

tWEW

MWEX

Vcc < 4.5V

MCLK×n-3

-

ns

Vcc ≥ 4.5V

MCLK×m+9

MWEX ↑ → Address

output delay time

tWEH - AX

MWEX

MAD[24:0]

Vcc < 4.5V

0

MCLK×m+12

ns

Vcc ≥ 4.5V

MCLK×n-9

MCLK×n+9

MCSX ↓ →

MWEX ↓ delay time

tCSL - WEL

Vcc < 4.5V

MCLK×n-12 MCLK×n+12

ns

Vcc ≥ 4.5V

MCLK×m+9

MWEX ↑→

MCSX ↑ delay time

tWEH - CSH

MWEX

MCSX[7:0]

Vcc < 4.5V

0

MCLK×m+12

ns

Vcc ≥ 4.5V

MCLK×n-9

MCLK×n+9

MCSX ↓ →

MDQM ↓ delay time

tCSL-WDQML

MCSX

MDQM[1:0]

Vcc < 4.5V

MCLK×n-12 MCLK×n+12

ns

Vcc ≥ 4.5V

- 9

9

MWEX ↓ →

Data output time

tWEL - DV

Vcc < 4.5V

-12

12

ns

Vcc ≥ 4.5V

MCLK×m+9

MWEX ↑ →

Data hold time

tWEH - DX

MWEX

MADATA[15:0]

Vcc < 4.5V

0

MCLK×m+12

ns

Note: When the external load capacitance = 30pF (m = 0 to 15, n = 1 to 16).

相關PDF資料 |

PDF描述 |

|---|---|

| MB9AF114LPMC | RISC MICROCONTROLLER, PQFP64 |

| MB9AF112MPMC | RISC MICROCONTROLLER, PQFP80 |

| MB9AF112LPMC1 | RISC MICROCONTROLLER, PQFP64 |

| MB9AF112NPMC | RISC MICROCONTROLLER, PQFP100 |

| MB9AF111NPF | RISC MICROCONTROLLER, PQFP100 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MB9AF114LAPMC1-G-JNE2 | 制造商:Fujitsu 功能描述:Bulk |

| MB9AF114LPMC1-GE1 | 制造商:FUJITSU 功能描述: |

| MB9AF114LPMC1-G-JNE1 | 制造商:FUJITSU 功能描述: 制造商:FUJITSU 功能描述:MCU 32BIT CORTEX-M3 FM3 64LQFP |

| MB9AF114MAPMC-G-JNE2 | 制造商:Fujitsu 功能描述:Bulk |

| MB9AF114MPMC-G-JNE1 | 制造商:FUJITSU 功能描述:MCU 32BIT CORTEX-M3 FM3 80LQFP |

發(fā)布緊急采購,3分鐘左右您將得到回復。