- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382288 > MB87M2141 (Fujitsu Limited) MPEG-2 Decoder for Set-Top-Boxes PDF資料下載

參數(shù)資料

| 型號(hào): | MB87M2141 |

| 廠商: | Fujitsu Limited |

| 英文描述: | MPEG-2 Decoder for Set-Top-Boxes |

| 中文描述: | 的MPEG - 2解碼器設(shè)置機(jī)頂盒 |

| 文件頁數(shù): | 1/2頁 |

| 文件大小: | 83K |

| 代理商: | MB87M2141 |

Copyright 2003 Fujitsu Microelectronics Europe GmbH Preliminary

Page 1 of 2

Disclaimer:

The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before

ordering.The information and circuit diagrams in this document are presented “as is”, no license is granted by implication or otherwise.

MB87M2141

Product Profile

January 2003

Edition 1.00

FME/MM/PP/0103

MPEG-2 Decoder for Set-Top-Boxes

SmartMPEG

TM

INTRODUCTION:

The

SmartMPEG

TM

is an integrated set-top-box

decoder. As a major component of a digital video

broadcast (DVB) set-top-box or IDTV this device

uses Fujitsu’s industry-leading Cx81 CMOS

technology (0.18μm).

It incorporates an ARC Tangent A4 RISC core

(@130MHz), two transport stream demultiplexers

with integrated DVB descramblers, a PAL/NTSC

digital video encoder and a display controller, which

overlays up to four layers of OSD. This set-top-box

decoder consists of a shared memory interface for

CPU and for MPEG decoding. The universal

processor interface allows connection to FLASH,

hard disk drives and other asynchronous devices.

The minimum SDRAM required is one 64Mbit

device using 16bit data bus.

The

SmartMPEG

TM

is the 3rd generation of

Fujitsu’s MPEG decoder, the successor to the

MB87L2250. With the MB87L2250, Fujitsu offered a

set-top-box chip, which enabled very low end

product cost. Its successor, the

SmartMPEG

TM

incorporates all the features which are required for

standard set-top-boxes. This high level of

integration makes it ideally suited for todays

interactive set-top-box applications.

Furthermore the Fujitsu Application Programming

Interface (FAPI) ensures a short time-to-market by

making the software development easier. The FAPI

is the programming interface for Fujitsu DVB

components as well as easing migration to future

devices.

FEATURES

MPEG2 video ISO/IEC 13818-2 (MP@ML...SP@ML)

MPEG audio layer 1/2

32-bit RISC CPU (ARC Tangent A4 @130MHz)

4K I-cache / 2K D-cache

Three timers / watchdog / power-down mode

Shared memory interface (SDRAM, 16/32 bit data),

64Mbit...1Gbit

Universal processor interface (IDE, NAND/NOR

FLASH & Common Interface)

Two transport stream decoders (decoding/recording)

including DVB descrambler

Flexible MPEG video resizing (factor 1/16 to 2)

Display controller with up to four true colour graphic or

CLUT layers

Teletext / WSS / CC / VBID insertion

PAL/NTSC digital encoder

RGB De-matrix (RGB or YCrCb output)

Control of brightness, contrast and colour saturation of

RGB and YCrCb output

5 video DAC’s @ 10bit

ITU-R 656 video input/output (shared with TS2 input)

S/P DIF output for PCM/AC3/MPEG

UART / Smart Card IF / I2C / GPIO

7-segment LED controller for 4 digits

Infra Red receiver / transmitter

PWM Output

On-chip DPLL, requiring only 27.0MHz crystal

Bootable from NOR Flash or I2C

FPT-208P-M06 (LQFP-Package)

Ambient Temperature Range (Std Pkg): 0

o

C to +70

o

C

Advanced Technology: Fujitsu CMOS Cx81 (0.18μm)

1.8 volt device with 3.3 volt I/O

Power consumption: typ. 800mW

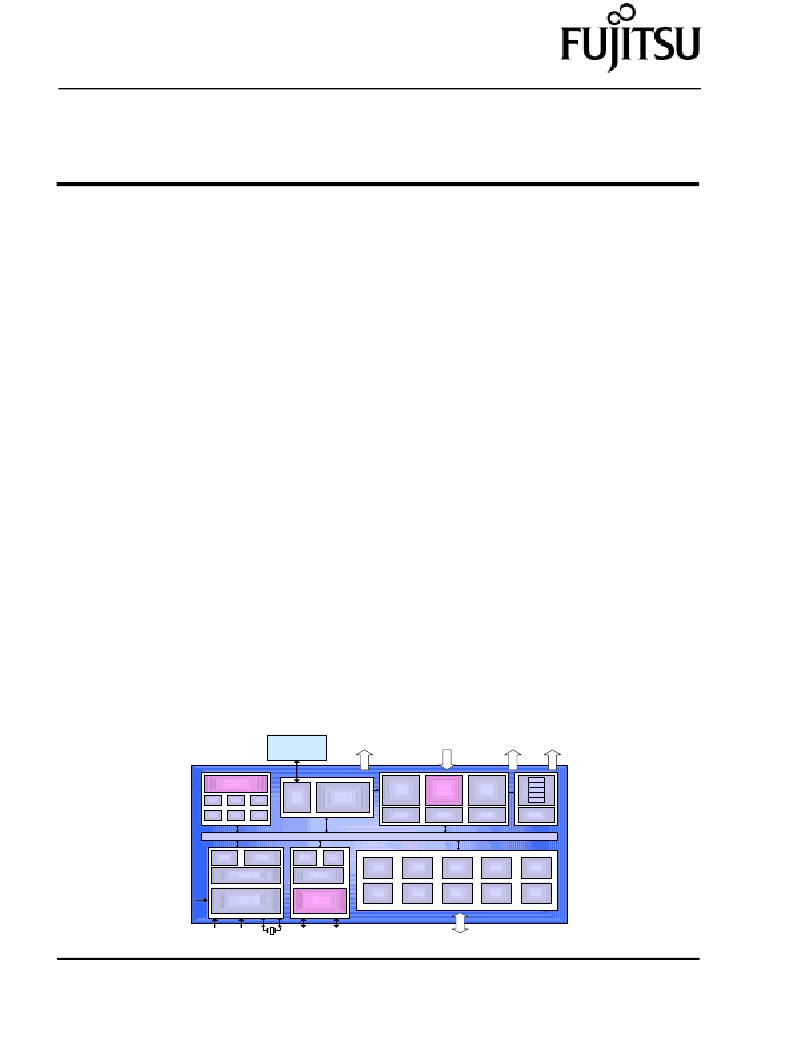

SmartMPEG Internal Bus @ 130.5MHz

ARC@ 130.5MHz

Tangent-A4

4K

I-Cache

2K

D-Cache

Watch-

Dog

Power-

Down

IRQ

CTRL

3

Timers

TS Demultiplexers

Buffer Mgr

DVB Descramblers

DPLL

S hared

Memory

Interface

MPE G-2 Video Decoder

MPE G Audio Decoder

S /P-DIF Output Unit

Resizing

TXT Insertion

Display

Controller

(4 Layer)

Digital

E ncoder

(PAL/NTSC)

Adjustable

RGB De-Matrix

WS S / VPS

Insertion

CC/VBID

Insertion

ITU-R656

Output

DAC1

DAC2

DAC3

DAC4

DAC5

Universal

Processor

Interface

Chip S elect

CTRL

HDD/IDE

CTRL

I2C

UART

Smart

Card

PWM

IR Rx

IR Tx

GPIO

GPI

GPO

7-Seg

CTRL

TS 1

Par/Ser

TS 2

Par/Ser

NOR / NAND Flash

HDD / IDE / CI

SDRAM

(64Mbit … 1Gbit)

16 / 32bit

S hared Memory

S /P-DIF

(Dolby Dig. Bitstream)

I2S (Audio)

Analog O/P:

CVBS , YC, RGB

Y C

R

C

B,

Audio R/L

ITU-R656

IRQ / I2C / S mart Card

UART / IR In / IR Out

GPIO / 7-S egment Ctrl

PWM / KeyBoard Mon

27.0MHz

TS 3

intern

ITU-R656

Boot

ROM

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MB89202P-SH | 8-Bit Proprietary Microcontroller |

| MB89202PFV | 8-Bit Proprietary Microcontroller |

| MB89F202 | 8-Bit Proprietary Microcontroller |

| MB89F202P-SH | 8-Bit Proprietary Microcontroller |

| MB89F202PFV | 8-Bit Proprietary Microcontroller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MB87M8412BGL-GE1 | 制造商:FUJITSU 功能描述: |

| MB87P2020 | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:Colour LCD/CRT/TV Controller |

| MB87P2020-A | 制造商:FUJITSU 功能描述: |

| MB87P2020-AE1 | 制造商:FUJITSU 功能描述: |

| MB87P2020PMT-ES-BND-DL | 制造商:FUJITSU 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。