- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45178 > MAXQ618J-0000+ (MAXIM INTEGRATED PRODUCTS INC) 16-BIT, FLASH, 12 MHz, RISC MICROCONTROLLER, QCC44 PDF資料下載

參數(shù)資料

| 型號: | MAXQ618J-0000+ |

| 廠商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 16-BIT, FLASH, 12 MHz, RISC MICROCONTROLLER, QCC44 |

| 封裝: | 7 X 7 MM, ROHS COMPLIANT, TQFN-44 |

| 文件頁數(shù): | 4/26頁 |

| 文件大小: | 1970K |

| 代理商: | MAXQ618J-0000+ |

Maxim Integrated Products 12

MAXQ618

16-Bit Microcontroller with Infrared Module

Memory

The microcontroller incorporates several memory types:

80KBflashmemory

2KBSRAMdatamemory

1.5KButilityROM

Softstack

Stack Memory

The device provides a soft stack that can be used to store

program return addresses (for subroutine calls and inter-

rupt handling) and other general-purpose data. This soft

stack is located in the 2KB SRAM data memory, which

means that the SRAM data memory must be shared

between the soft stack and general-purpose application

data storage. However, the location and size of the soft

stack is determined by the user, providing maximum

flexibility when allocating resources for a particular appli-

cation. The stack is used automatically by the processor

when the CALL, RET, and RETI instructions are executed

and when an interrupt is serviced. An application can

also store and retrieve values explicitly using the stack by

means of the PUSH, POP, and POPI instructions.

The SP pointer indicates the current top of the stack,

which initializes by default to the top of the SRAM data

memory. As values are pushed onto the stack, the SP

pointer decrements, which means that the stack grows

downward towards the bottom (lowest address) of the

data memory. Popping values off the stack causes the

SP pointer value to increase. Refer to the MAXQ610

User’s Guide for more details.

Utility ROM

The utility ROM is a 1.5KB block of internal ROM memory

located in program space beginning at address 8000h.

This ROM includes the following routines:

Productiontestroutines(internalmemorytests,mem-

ory loader, etc.), which are used for internal testing

only, and are generally of no use to the end-applica-

tion developer

User-callable routines for buffer copying and fast

table lookup (more information on these routines can

be found in the MAXQ610 User’s Guide)

Following any reset, execution begins in the utility ROM

at address 8000h. At this point, unless test mode has

been invoked (which requires special programming

through the JTAG interface), the utility ROM in the device

always automatically jumps to location 0000h, which is

the beginning of user application code.

Watchdog Timer

The internal watchdog timer greatly increases system

reliability. The timer resets the device if software execu-

tion is disturbed. The watchdog timer is a free-running

counter designed to be periodically reset by the appli-

cation software. If software is operating correctly, the

counter is periodically reset and never reaches its maxi-

mum count. However, if software operation is interrupted,

the timer does not reset, triggering a system reset and

optionally a watchdog timer interrupt. This protects the

system against electrical noise or electrostatic discharge

(ESD) upsets that could cause uncontrolled processor

operation. The internal watchdog timer is an upgrade to

older designs with external watchdog devices, reducing

system cost and simultaneously increasing reliability.

The watchdog timer functions as the source of both the

watchdog timer timeout and the watchdog timer reset.

The timeout period can be programmed in a range of

215 to 224 system clock cycles. An interrupt is gener-

ated when the timeout period expires if the interrupt

is enabled. All watchdog timer resets follow the pro-

grammed interrupt timeouts by 512 system clock cycles.

If the watchdog timer is not restarted for another full

interval in this time period, a system reset occurs when

the reset timeout expires. See Table 1.

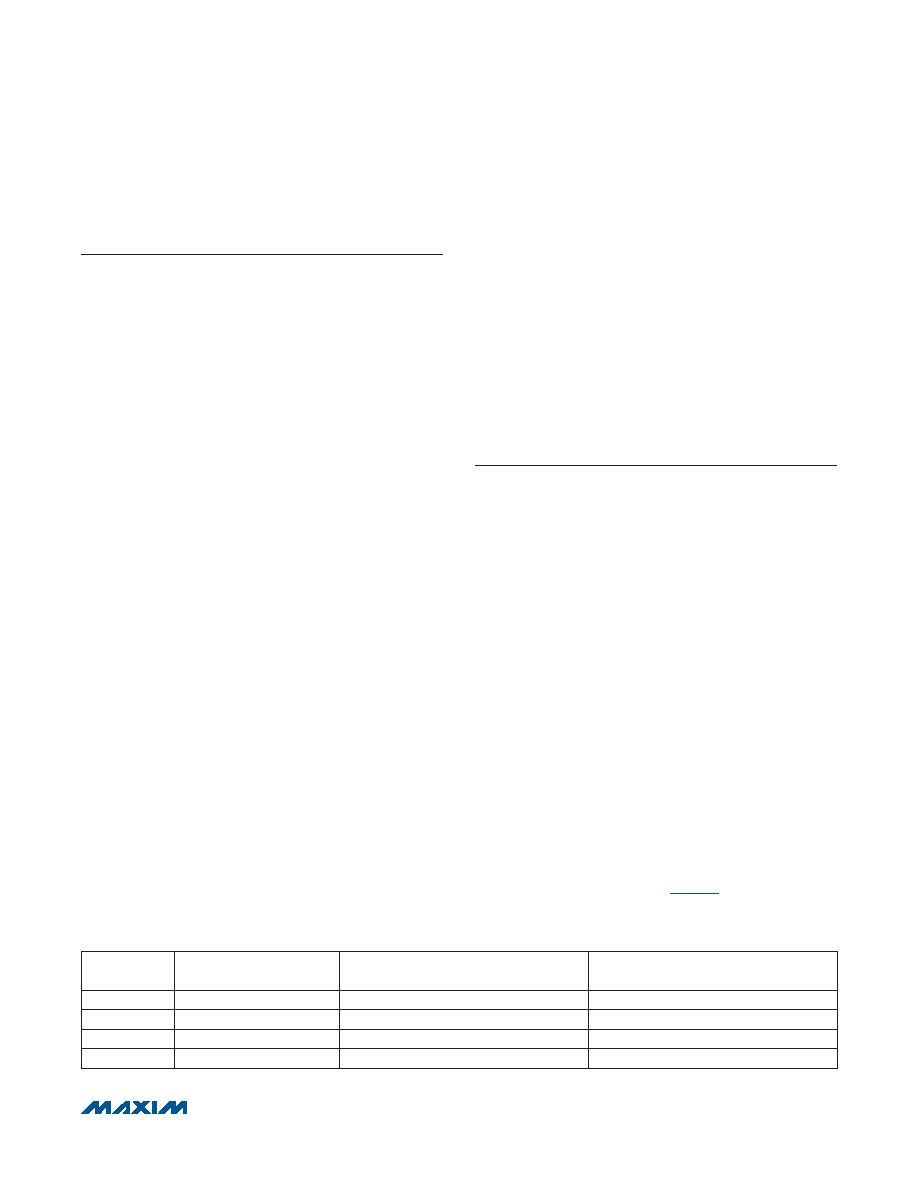

Table 1. Watchdog Interrupt Timeout (Sysclk = 12MHz, CD[1:0] = 00)

WD[1:0]

WATCHDOG CLOCK

WATCHDOG INTERRUPT TIMEOUT

WATCHDOG RESET AFTER

WATCHDOG INTERRUPT (s)

00

Sysclk/215

2.7ms

42.7

01

Sysclk/218

21.9ms

42.7

10

Sysclk/221

174.7ms

42.7

11

Sysclk/224

1.4s

42.7

相關PDF資料 |

PDF描述 |

|---|---|

| MAZD02400L | 2.4 V, 0.12 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE |

| MAZD03000L | 3 V, 0.12 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE |

| MAZD22000L | 22 V, 0.12 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE |

| MAZD12000L | 12 V, 0.12 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE |

| MAZD10000L | 10 V, 0.12 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE |

相關代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAXQ618J-0000+ | 功能描述:16位微控制器 - MCU 16-Bit MCU w/Infrared Module RoHS:否 制造商:Texas Instruments 核心:RISC 處理器系列:MSP430FR572x 數(shù)據(jù)總線寬度:16 bit 最大時鐘頻率:24 MHz 程序存儲器大小:8 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:2 V to 3.6 V 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:VQFN-40 安裝風格:SMD/SMT |

| MAXQ618X-0000+ | 制造商:MAXIM 制造商全稱:Maxim Integrated Products 功能描述:16-Bit Microcontroller with Infrared Module |

| MAXQ61C | 制造商:MAXIM 制造商全稱:Maxim Integrated Products 功能描述:16-Bit Microcontroller with Infrared Module |

| MAXQ61CA | 制造商:MAXIM 制造商全稱:Maxim Integrated Products 功能描述:16-Bit Microcontroller with Infrared Module |

| MAXQ61CE | 制造商:MAXIM 制造商全稱:Maxim Integrated Products 功能描述:16-Bit Microcontroller with Infrared Module |

發(fā)布緊急采購,3分鐘左右您將得到回復。