- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384656 > MAX2360 (Maxim Integrated Products, Inc.) Quadruple Bus Buffer Gates With 3-State Outputs 14-PDIP -40 to 85 PDF資料下載

參數(shù)資料

| 型號(hào): | MAX2360 |

| 廠商: | Maxim Integrated Products, Inc. |

| 英文描述: | Quadruple Bus Buffer Gates With 3-State Outputs 14-PDIP -40 to 85 |

| 中文描述: | 完備的雙頻段正交發(fā)送器 |

| 文件頁數(shù): | 13/24頁 |

| 文件大小: | 413K |

| 代理商: | MAX2360 |

M

Complete Dual-Band

Quadrature Transmitters

______________________________________________________________________________________

13

Electromagnetic

Compliance Considerations

Two major concepts should be employed to produce a

noise-free and EMC-compliant transmitter: minimize cir-

cular current-loop area to reduce H-field radiation and

minimize voltage drops to reduce E-field radiation. To

minimize circular current-loop area, bypass as close to

the part as possible and use the distributed capaci-

tance of a ground plane. To minimize voltage drops,

make V

CC

traces short and wide, and make RF traces

short.

The “don't care” bits in the registers should be “0” in

order to minimize electromagnetic radiation due to

unnecessary bit banging. RC filtering can also be used

to slow the clock edges on the 3-wire interface, reduc-

ing high-frequency spectral content. RC filtering also

provides for transient protection against IEC802 testing

by shunting high frequencies to ground, while the

series resistance attenuates the transients for error-free

operation. The same applies to the override pins

(

SHDN

,

TXGATE

,

IDLE

).

High-frequency bypass capacitors are required close

to the pins with a dedicated via to ground. The 48-pin

TQFP-EP package provides minimal inductance ground

by using an exposed paddle under the part. Provide at

least five low-inductance vias under the paddle to

ground, to minimize ground inductance. Use a solid

ground plane wherever possible. Any cutout in the

ground plane may act as slot radiator and reduce its

shield effectiveness.

Keep the RF LO traces as short as possible to reduce

LO radiation and susceptibility to interference.

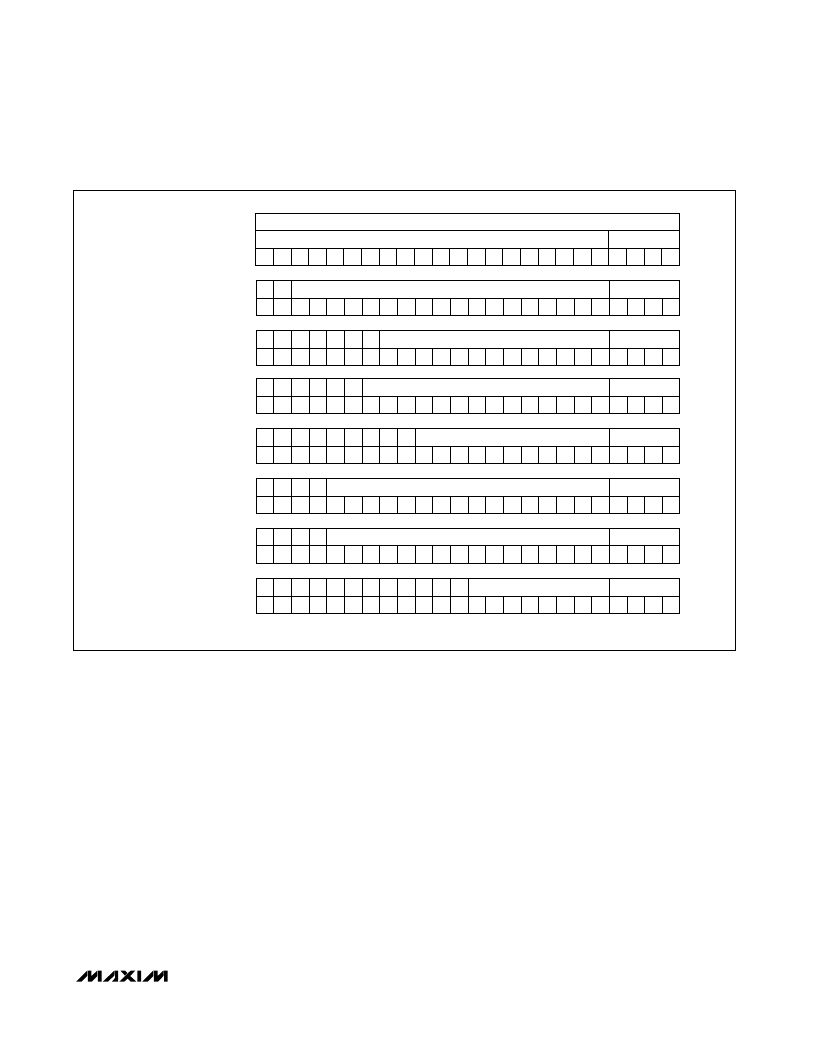

Figure 1. Register Configuration

MSB

24 BIT REGISTER

LSB

DATA 20 BITS

ADDRESS 4 BITS

B18

B16

B19

B17

B14

B12

B15

B13

B10

B8

B11

B9

B6

B4

B7

B5

B2

B0

B3

B1

A2

A0

A3

A1

RFM DIVIDE RATIO (18)

ADDRESS

X

B16

X

B17

B14

B12

B15

B13

B10

B8

B11

B9

B6

B4

B7

B5

B2

B0

B3

B1

0

0

0

0

RFM DIVIDE REGISTER

RFR DIVIDE RATIO (13)

ADDRESS

X

X

X

X

X

B12

X

X

B10

B8

B11

B9

B6

B4

B7

B5

B2

B0

B3

B1

0

1

0

0

RFR DIVIDE REGISTER

IFM DIVIDE RATIO (14)

ADDRESS

X

X

X

X

X

B12

X

B13

B10

B8

B11

B9

B6

B4

B7

B5

B2

B0

B3

B1

0

0

0

1

IFM DIVIDE REGISTER

RFR DIVIDE RATIO (11)

ADDRESS

X

X

X

X

X

X

X

X

B10

B8

X

B9

B6

B4

B7

B5

B2

B0

B3

B1

0

1

0

1

IFR DIVIDE REGISTER

CONTROL BITS (16)

ADDRESS

X

X

X

X

B14

B12

B15

B13

B10

B8

B11

B9

B6

B4

B7

B5

B2

B0

B3

B1

1

0

0

0

CONTROL REGISTER

CONFIGURATION BITS (16)

ADDRESS

X

X

X

X

B14

B12

B15

B13

B10

B8

B11

B9

B6

B4

B7

B5

B2

B0

B3

B1

1

1

0

0

CONFIGURATION REGISTER

TEST BITS (8)

ADDRESS

X

X

X

X

X

X

X

X

X

X

X

X

B6

B4

B7

B5

B2

B0

B3

B1

1

1

0

1

TEST REGISTER

X = DON

’

T CARE

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MAX2360ECM | Quadruple Bus Buffer Gates With 3-State Outputs 14-PDIP -40 to 85 |

| MAX2362ECM | Quadruple Bus Buffer Gates With 3-State Outputs 14-SO -40 to 85 |

| MAX2364ECM | Quadruple Bus Buffer Gates With 3-State Outputs 14-SO -40 to 85 |

| MAX2402EAP | Analog IC |

| MAX2430ISE | Low-Voltage, Silicon RF Power Amplifier/Predriver |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAX2360ECM | 功能描述:射頻發(fā)射器 RoHS:否 制造商:Micrel 類型:ASK Transmitter 封裝 / 箱體:SOT-23-6 工作頻率:300 MHz to 450 MHz 封裝:Reel |

| MAX2360ECM-T | 功能描述:射頻發(fā)射器 RoHS:否 制造商:Micrel 類型:ASK Transmitter 封裝 / 箱體:SOT-23-6 工作頻率:300 MHz to 450 MHz 封裝:Reel |

| MAX2360EVKIT | 功能描述:射頻開發(fā)工具 RoHS:否 制造商:Taiyo Yuden 產(chǎn)品:Wireless Modules 類型:Wireless Audio 工具用于評(píng)估:WYSAAVDX7 頻率: 工作電源電壓:3.4 V to 5.5 V |

| MAX2361ECM | 功能描述:射頻發(fā)射器 RoHS:否 制造商:Micrel 類型:ASK Transmitter 封裝 / 箱體:SOT-23-6 工作頻率:300 MHz to 450 MHz 封裝:Reel |

| MAX2361ECM+ | 功能描述:射頻發(fā)射器 RoHS:否 制造商:Micrel 類型:ASK Transmitter 封裝 / 箱體:SOT-23-6 工作頻率:300 MHz to 450 MHz 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。