- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385520 > MAX1083BEUE (MAXIM INTEGRATED PRODUCTS INC) 300ksps/400ksps, Single-Supply, 4-Channel, Serial 10-Bit ADCs with Internal Reference PDF資料下載

參數(shù)資料

| 型號: | MAX1083BEUE |

| 廠商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分類: | ADC |

| 英文描述: | 300ksps/400ksps, Single-Supply, 4-Channel, Serial 10-Bit ADCs with Internal Reference |

| 中文描述: | 4-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO16 |

| 封裝: | 4.40 MM, 0.65MM PITCH, MO-153AC, TSSOP-16 |

| 文件頁數(shù): | 11/24頁 |

| 文件大小: | 315K |

| 代理商: | MAX1083BEUE |

Detailed Description

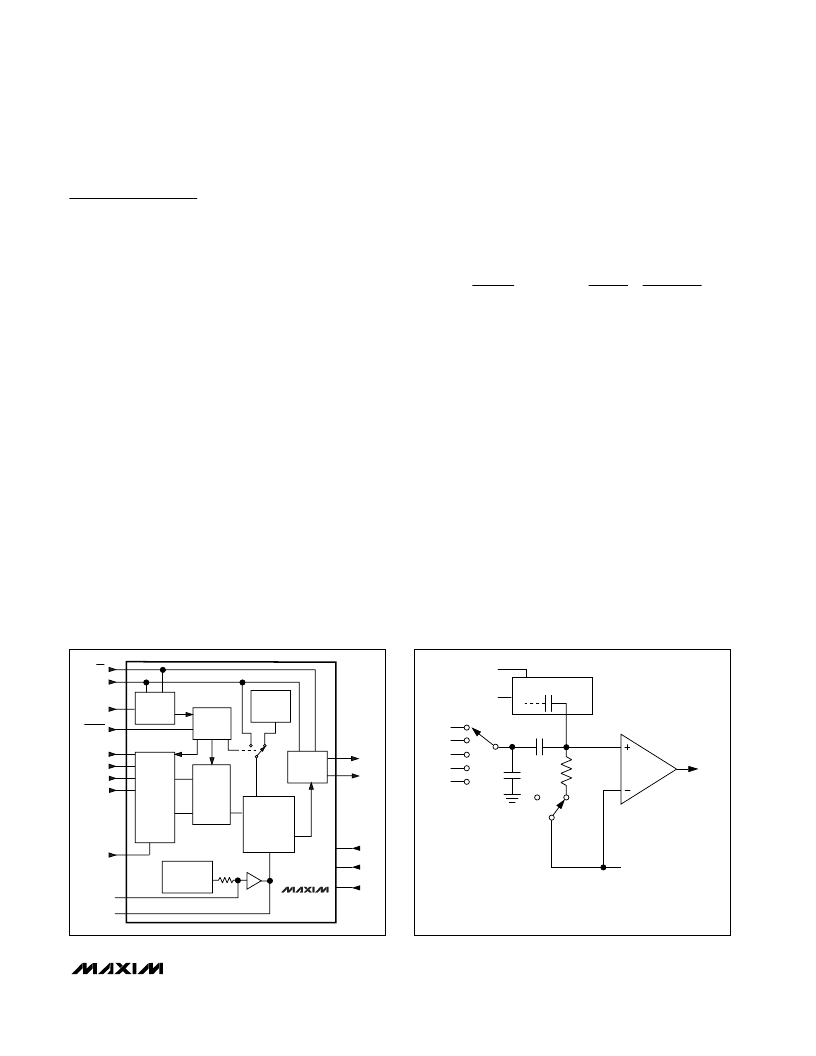

The MAX1082/MAX1083 ADCs use a successive-

approximation conversion technique and input T/H cir-

cuitry to convert an analog signal to a 10-bit digital out-

put. A flexible serial interface provides easy interface to

microprocessors (μPs). Figure 3 shows a functional dia-

gram of the MAX1082/MAX1083.

Pseudo-Differential Input

The equivalent circuit of Figure 4 shows the MAX1082/

MAX1083’s input architecture, which is composed of a

T/H, input multiplexer, input comparator, switched-

capacitor DAC, and reference.

In single-ended mode, the positive input (IN+) is con-

nected to the selected input channel and the negative

input (IN-) is set to COM. In differential mode, IN+ and

IN- are selected from the following pairs: CH0/CH1 and

CH2/CH3. Configure the channels according to Tables

1 and 2.

The MAX1082/MAX1083 input configuration is pseudo-

differential because only the signal at IN+ is sampled.

The return side (IN-) is connected to the sampling

capacitor while converting and must remain stable

within ±0.5LSB (±0.1LSB for best results) with respect

to GND during a conversion.

If a varying signal is applied to the selected IN-, its

amplitude and frequency must be limited to maintain

accuracy. The following equations express the relation-

ship between the maximum signal amplitude and its

frequency to maintain ±0.5LSB accuracy. Assuming a

sinusoidal signal at IN-, the input voltage is determined

by:

V

V

IN

IN

=

(

The maximum voltage variation is determined by:

A 2.6Vp-p, 60Hz signal at IN- will generate a ±0.5LSB

error when using a +2.5V reference voltage and a

2.5μs conversion time (15 / f

SCLK

). When a DC refer-

ence voltage is used at IN-, connect a 0.1μF capacitor

to GND to minimize noise at the input.

During the acquisition interval, the channel selected as

the positive input (IN+) charges capacitor C

HOLD

. The

acquisition interval spans three SCLK cycles and ends

on the falling SCLK edge after the input control word’s

last bit has been entered. At the end of the acquisition

interval, the T/H switch opens, retaining charge on

C

HOLD

as a sample of the signal at IN+. The conver-

sion interval begins with the input multiplexer switching

C

HOLD

from IN+ to IN-. This unbalances node ZERO at

the comparator’s input. The capacitive DAC adjusts

during the remainder of the conversion cycle to restore

node ZERO to V

DD1

/2 within the limits of 10-bit resolu-

tion. This action is equivalent to transferring a

12pF x (V

IN

+ - V

IN

-) charge from C

HOLD

to the binary-

weighted capacitive DAC, which in turn forms a digital

representation of the analog input signal.

max

(

)

d

dt

V

f

LSB

1

t

V

t

V

IN

CONV

REF

CONV

IN

=

≤

=

2

2

10

π

ft

)sin(

)

2

π

M

300ksps/400ksps, Single-Supply, 4-Channel,

Serial 10-Bit ADCs with Internal Reference

______________________________________________________________________________________

11

INPUT

SHIFT

REGISTER

CONTROL

LOGIC

INT

CLOCK

OUTPUT

SHIFT

REGISTER

+1.22V

REFERENCE

T/H

ANALOG

INPUT

MUX

10 + 2-BIT

SAR ADC

IN

DOUT

SSTRB

V

DD1

V

DD2

GND

SCLK

DIN

COM

REFADJ

REF

OUT

REF

CLOCK

+2.500V

17k

7

8

9

6

11

12

13

14

15

CH1

CH2

CH3

3

4

5

CH0

2

MAX1282

MAX1283

CS

SHDN

1

16

10

2.05

A

≈

Figure 3. Functional Diagram

C

HOLD

12pF

R

IN

800

HOLD

INPUT

MUX

C

SWITCH

*

*INCLUDES ALL INPUT PARASITICS

SINGLE-ENDED MODE: IN+ = CH0

–

CH3, IN- = COM.

PSEUDO-DIFFERENTIAL MODE: IN+ AND IN- SELECTED FROM

PAIRS OF CH0/CH1 AND CH2/CH3.

AT THE SAMPLING INSTANT,

THE MUX INPUT SWITCHES FROM

THE SELECTED IN+ CHANNEL TO

THE SELECTED IN- CHANNEL.

CH0

CH1

CH2

CH3

COM

REF

GND

ZERO

V

DD1

/2

COMPARATOR

CAPACITIVE

DAC

6pF

TRACK

Figure 4. Equivalent Input Circuit

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MAX109 | 8-Bit, 2.2Gsps ADC with Track/Hold Amplifier and 1:4 Demultiplexed LVDS Outputs |

| MAX109EHF-D | 8-Bit, 2.2Gsps ADC with Track/Hold Amplifier and 1:4 Demultiplexed LVDS Outputs |

| MAX1101 | Single-Chip, 8-Bit CCD Digitizer with Clamp and 6-Bit PGA |

| MAX1101CWG | Single-Chip, 8-Bit CCD Digitizer with Clamp and 6-Bit PGA |

| MAX11041 | Wired Remote Controllers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAX1083BEUE+ | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 300/400ksps Sgl-Sply 4Ch Serial 10Bit RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| MAX1083BEUE+T | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 300/400ksps Sgl-Sply 4Ch Serial 10Bit RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| MAX1083BEUE-T | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| MAX1084 | 制造商:MAXIM 制造商全稱:Maxim Integrated Products 功能描述:400ksps/300ksps, Single-Supply, Low-Power, Serial 10-Bit ADCs with Internal Reference |

| MAX1084ACSA | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC Integrated Circuits (ICs) RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。