- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359650 > MAC7132VVM50 (飛思卡爾半導(dǎo)體(中國)有限公司) Microcontroller Family Hardware Specifications PDF資料下載

參數(shù)資料

| 型號: | MAC7132VVM50 |

| 廠商: | 飛思卡爾半導(dǎo)體(中國)有限公司 |

| 英文描述: | Microcontroller Family Hardware Specifications |

| 中文描述: | 微控制器系列硬件規(guī)格 |

| 文件頁數(shù): | 26/56頁 |

| 文件大小: | 471K |

| 代理商: | MAC7132VVM50 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當(dāng)前第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁

MAC7100 Microcontroller Family Hardware Specifications, Rev. 1.2

Preliminary

Electrical Characteristics

Freescale Semiconductor

26

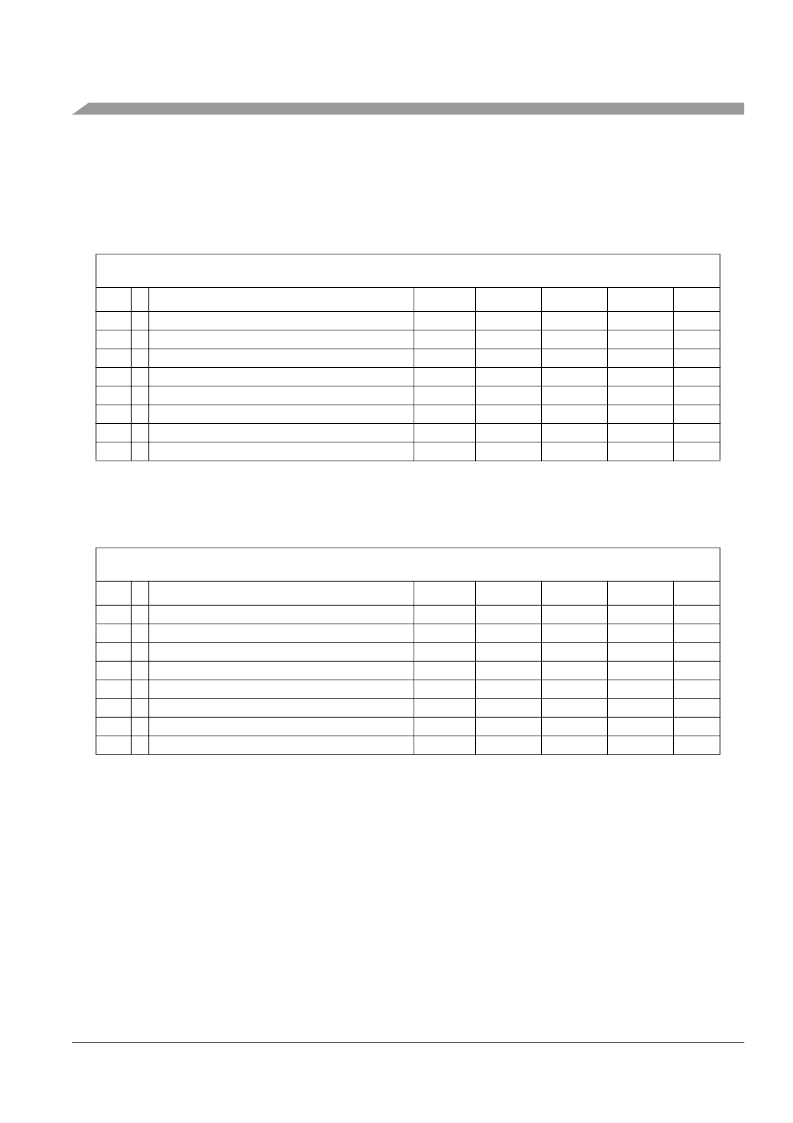

3.10.2 ATD Accuracy

Table 29

and

Table 30

specify the ATD conversion performance excluding any errors due to current

injection, input capacitance and source resistance.

For the following definitions, see

Figure 9

.

Differential Non-Linearity (DNL) is defined as the difference between two adjacent switching steps:

Eqn. 17

The Integral Non-Linearity (INL) is defined as the sum of all DNLs:

Eqn. 18

Table 29. ATD Conversion Performance in 5.0 V Range

Conditions shown in

Table 7

except as noted here:

f

ATDCLK

= 2.0 MHz, 4.5 V

≤

V

DD

A

≤

5.5 V

Num C

Rating

Symbol

Min

Typ

5

1

—

±

1.5

±

2.0

20

1

—

±

0.5

±

1.0

Max

Unit

R1

R2

R3

R4

R5

R6

R7

R8

P 10-bit Resolution

P 10-bit Differential Nonlinearity

P 10-bit Integral Nonlinearity

P 10-bit Absolute Error

2

P 8-bit Resolution

P 8-bit Differential Nonlinearity

P 8-bit Integral Nonlinearity

P 8-bit Absolute Error

2

LSB

DNL

INL

AE

LSB

DNL

INL

AE

—

–1

–2.5

–3

—

–0.5

–1.0

–1.5

NOTES:

1. Assumes V

REF

= V

RH

– V

RL

= 5.12 V, other V

REF

conditions result in different LSB resolutions.

2. These values include the quantization error which is inherently count for any A/D converter.

—

1

2.5

3

—

0.5

1.0

1.5

mV

Counts

Counts

Counts

mV

Counts

Counts

Counts

Table 30. ATD Conversion Performance in 3.3 V Range

Conditions shown in

Table 7

except as noted here:

f

ATDCLK

= 2.0 MHz, 3.15 V

≤

V

DD

A

≤

3.6 V

Num C

Rating

Symbol

Min

Typ

3.25

1

—

±

1.5

±

2.0

13

1

—

±

1.0

±

1.0

Max

Unit

S1

S2

S3

S4

S5

S6

S7

S8

P 10-bit Resolution

P 10-bit Differential Nonlinearity

P 10-bit Integral Nonlinearity

P 10-bit Absolute Error

2

P 8-bit Resolution

P 8-bit Differential Nonlinearity

P 8-bit Integral Nonlinearity

P 8-bit Absolute Error

2

LSB

DNL

INL

AE

LSB

DNL

INL

AE

—

–1.5

–3.5

–5

—

–0.5

–1.5

–1.5

NOTES:

1. Assumes V

REF

= V

RH

– V

RL

= 3.33 V, other V

REF

conditions result in different LSB resolutions.

2. These values include the quantization error which is inherently count for any A/D converter.

—

1.5

3.5

5

—

0.5

1.5

1.5

mV

Counts

Counts

Counts

mV

Counts

Counts

Counts

DNL i

( )

V

----------------------

V

1

–

–

1 LSB

1

–

=

INL n

DNL i

( )

i

1

=

n

∑

V

1 LSB

0

-------–

n

–

=

=

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MAC7136 | Microcontroller Family Hardware Specifications |

| MAC7136CAF50 | Microcontroller Family Hardware Specifications |

| MC68HC08JK8CP | Microcontrollers |

| MC68HC08JK8MDW | Microcontrollers |

| MC68HC08JK8MP | Microcontrollers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAC7134 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontroller Family Reference Manual |

| MAC7135 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontroller Family Reference Manual |

| MAC7136 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontroller Family Reference Manual |

| MAC7136CAF50 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontroller Family Hardware Specifications |

| MAC7136CAG50 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontroller Family Hardware Specifications |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。