-

[北京]010-87982920

-

[深圳]0755-82701186

- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45053 > M908-02I155.5200LF 155.52 MHz, OTHER CLOCK GENERATOR, CQCC36 PDF資料下載

參數(shù)資料

| 型號: | M908-02I155.5200LF |

| 元件分類: | 時(shí)鐘產(chǎn)生/分配 |

| 英文描述: | 155.52 MHz, OTHER CLOCK GENERATOR, CQCC36 |

| 封裝: | 9 X 9 MM, CERAMIC, LCC-36 |

| 文件頁數(shù): | 4/6頁 |

| 文件大小: | 295K |

| 代理商: | M908-02I155.5200LF |

M908-02 Datasheet Rev 0.4

4 of 6

Revised 30Jul2004

I n teg r at ed Circuit Systems , Inc. ● Netw o r ki ng & C o mmun ica t io ns ● ww w. icst.com ● te l (5 08 ) 8 5 2 - 54 00

M908-02

VCSO BASED CLOCK GENERATOR

Preliminar y In f o r m atio n

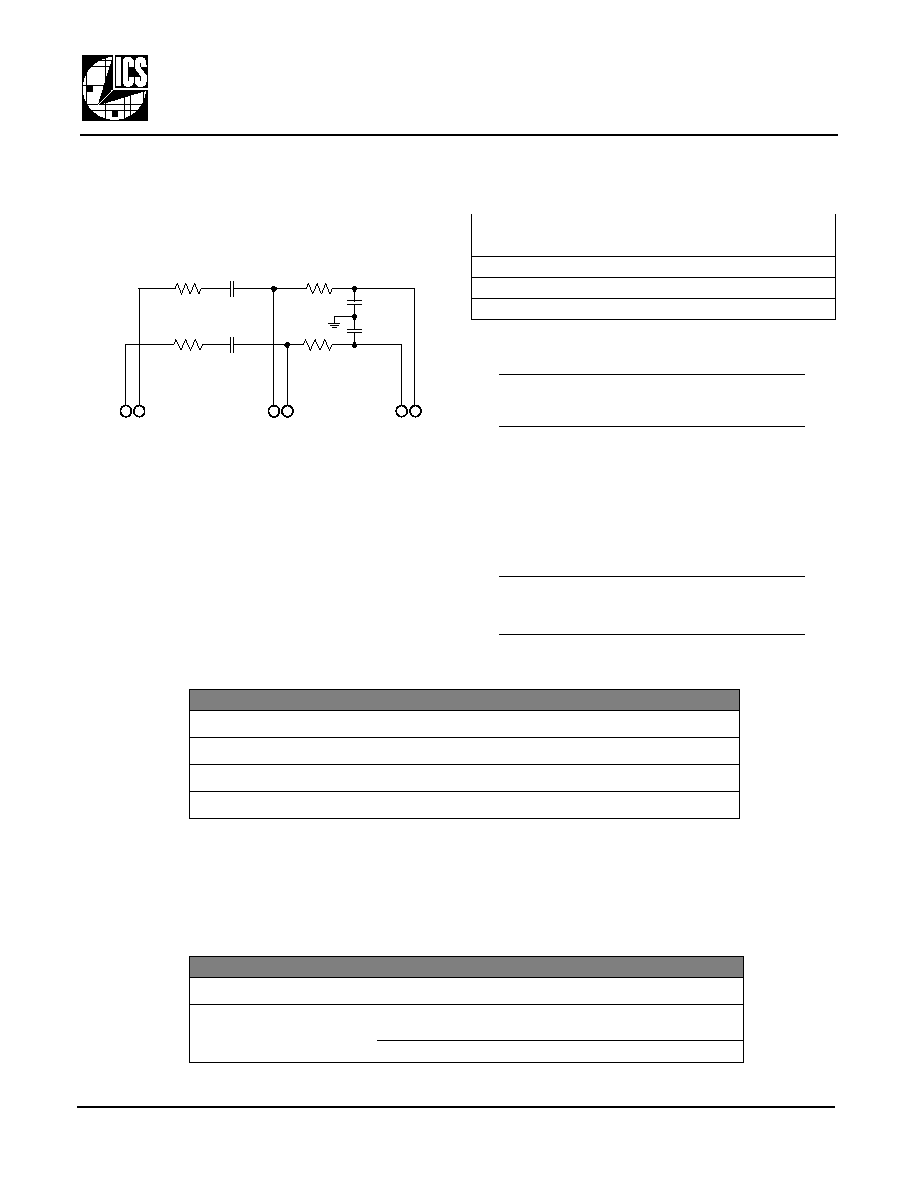

External Loop Filter

To provide stable PLL operation, and thereby a low jitter

output clock, the M908-02 requires the use of an

external loop filter. This is provided via the provided

filter pins (see Figure 5).

Figure 5: External Loop Filter

The loop filter is implemented as a differential circuit

to minimize system noise interference. Due to the

differential signal path design, the implementation

requires two identical complementary RC filters as

shown here.

Values, below.

additional product information.

PLL Simulator Tool Available

for additional information.

C

POST

C

POST

VC

nVC

R

POST

nOP_OUT

OP_OUT

R

POST

R

LOOP

R

LOOP

C

LOOP

C

LOOP

OP_IN

nOP_IN

Example External Loop Filter Component Values

PLL Bandwidth

(kHz)

Damping

Factor

R loop

(k

)

C loop

(

F)

R post

(k

)

C post

(pF)

0.395

2.0

1.5

4.70

20

3300

1.2

2.9

4.7

1.00

20

1000

10

1

Note 1: Recommended for minimum output jitter when

using a crystal or crystal oscillator reference.

2.4

39.0

0.01

20

240

ABSOLUTE MAXIMUM RATINGS1

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the

device. These ratings are stress specifications only. Functional operation of product at these conditions

or any conditions beyond those listed in Recommended Conditions of Operation, DC Characteristics, or

AC Characteristics is not implied. Exposure to absolute maximum rating conditions for extended periods

may affect product reliability.

Symbol Parameter

Rating

Unit

V

I

Inputs

-0.5 to V

CC +0.5

V

O

Outputs

-0.5 to V

CC +0.5

V

CC

Power Supply Voltage

4.6

V

T

S

Storage Temperature

-45 to +100

oC

Table 5: Absolute Maximum Ratings

RECOMMENDED CONDITIONS OF OPERATION

Symbol Parameter

Min

Typ

Max

Unit

V

CC

Positive Supply Voltage

3.135

3.3

3.465

V

T

A

Ambient Operating Temperature

Commercial

0

+70

oC

Industrial

-40

+85

oC

Table 6: Recommended Conditions of Operation

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M908-02-155.5200LF | 155.52 MHz, OTHER CLOCK GENERATOR, CQCC36 |

| M908-02I175.0000 | 175 MHz, OTHER CLOCK GENERATOR, CQCC36 |

| M908-02I155.5200 | 155.52 MHz, OTHER CLOCK GENERATOR, CQCC36 |

| M926-02I600.0000LF | 600 MHz, OTHER CLOCK GENERATOR, CQCC36 |

| M926-02-622.0800LF | 622.08 MHz, OTHER CLOCK GENERATOR, CQCC36 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M9081 | 制造商:Tamura Corporation of America 功能描述: |

| M9088 | 制造商:Motorola Inc 功能描述: |

| M9099 | 制造商:Tamura Corporation of America 功能描述: |

| M90C-1006 | 制造商:Teledyne Relays 功能描述: |

| M90C109095C-08 | 制造商:Harwin 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。

- VIP會(huì)員服務(wù) |

- 廣告服務(wù) |

- 付款方式 |

- 聯(lián)系我們 |

- 招聘銷售 |

- 免責(zé)條款 |

- 網(wǎng)站地圖