- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45053 > M8813F3W-15K1 (STMICROELECTRONICS) 1M X 1 FLASH, 27 I/O, PIA-GENERAL PURPOSE, PQCC52 PDF資料下載

參數(shù)資料

| 型號: | M8813F3W-15K1 |

| 廠商: | STMICROELECTRONICS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 1M X 1 FLASH, 27 I/O, PIA-GENERAL PURPOSE, PQCC52 |

| 封裝: | PLASTIC, LCC-52 |

| 文件頁數(shù): | 33/85頁 |

| 文件大小: | 601K |

| 代理商: | M8813F3W-15K1 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁當前第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁

39/85

M88 FAMILY

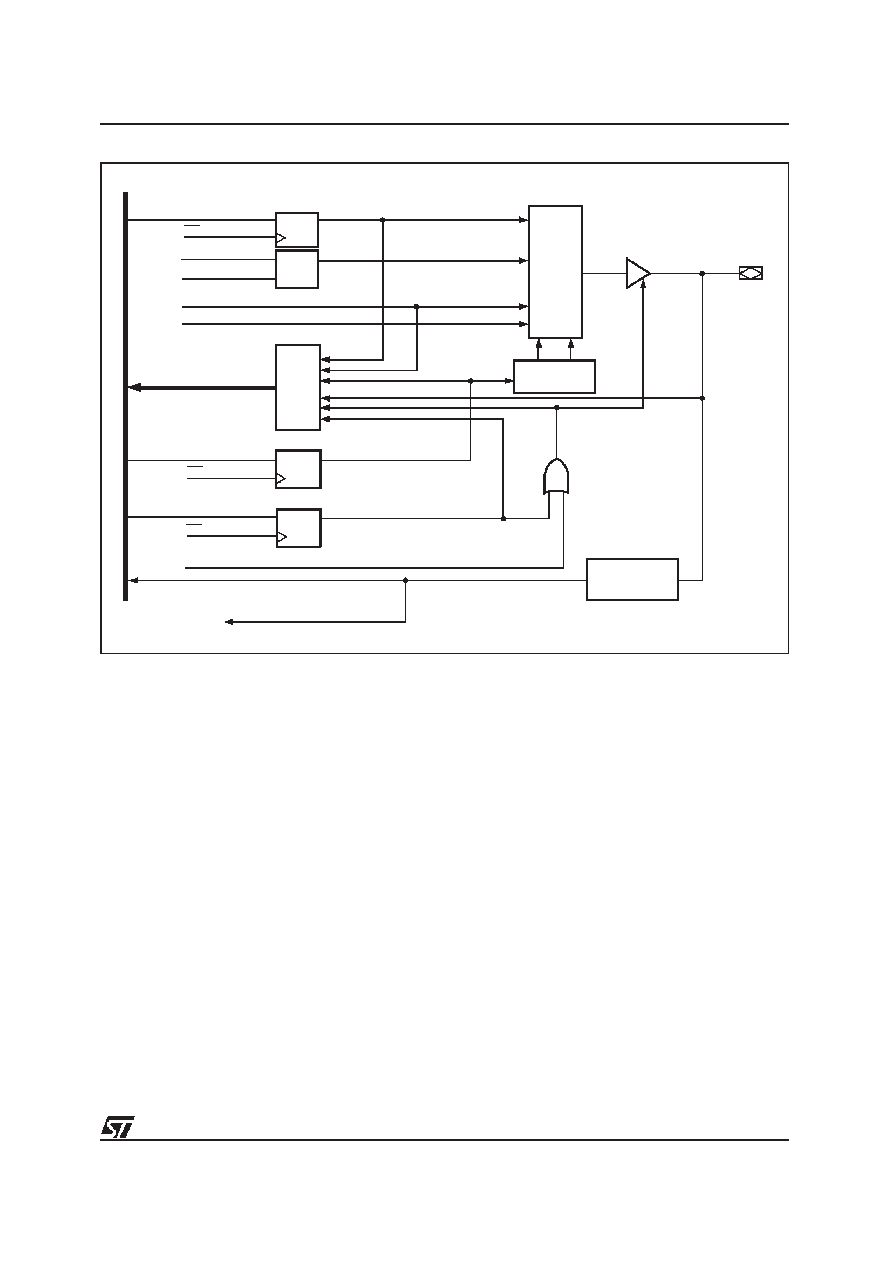

Figu re 27. General I/O Port Architecture

INTERNAL

DATA

BUS

DATA OUT

REG.

DQ

D

G

Q

DQ

WR

ADDRESS

MACROCELL OUTPUTS

ENABLE PRODUCT TERM (.OE)

EXT CS

ALE

READ MUX

P

D

B

CPLD- INPUT

CONTROL REG.

DIR REG.

INPUT

MACROCELL

ENABLE OUT

DATA IN

OUTPUT

SELECT

OUTPUT

MUX

PORT PIN

DATA OUT

ADDRESS

AI02885

have burst cycles. Address bits A[3:0] are not

multiplexed, while A[19:4] are multiplexed with

data bits D[15:0] in 16-bit mode. In 8-bit mode,

A[11:4] are multiplexed with data bits D[7:0].

The 80C51XA can be configured to operate in

eight-bit data mode. (shown in Figure 25).

The 80C51XA improves bus throughput and

performance by executing Burst cycles for code

fetches. In Burst Mode, address A19-4 are latched

internally by the M88x3Fxx FLASH+PSD, while

the 80C51XA changes the A3-0 lines to fetch up to

16 bytes of code. The PSD access time is then

measured from address A3-A0 valid to data in

valid. The PSD bus timing requirement in Burst

Mode is identical to the normal bus cycle, except

the address setup and hold time with respect to

ALE does not apply.

68HC11

Figure 26 shows an interface to a 68HC11 where

the M8813F1x is configured in 8-bit multiplexed

mode with E and R/W settings. The DPLD can

generate the READ and WR signals for external

devices.

I/O Ports

There are four programmable I/O ports: Ports A, B,

C, and D. Each of the ports is eight bits except Port

D, which is 3 bits. Each port pin is individually user

configurable, thus allowing multiple functions per

port. The ports are configured using PSDsoft

Configuration or by the microcontroller writing to

on-chip registers in the CSIOP address space.

The topics discussed in this section are:

s

General Port Architecture

s

Port Operating Modes

s

Port Configuration Registers

s

Port Data Registers

s

Individual Port Functionality.

General Port Architecture

The general architecture of the I/O Port is shown

in Figure 27. Individual Port architectures are

shown in Figure 29 to Figure 32. In general, once

the purpose for a port pin has been defined, that

pin will no longer be available for other purposes.

Exceptions will be noted.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M8813F3Y-90K1 | 1M X 1 FLASH, 27 I/O, PIA-GENERAL PURPOSE, PQCC52 |

| M8813F3Y-90T1 | 1M X 1 FLASH, 27 I/O, PIA-GENERAL PURPOSE, PQFP52 |

| M8803F3Y-90K1T | 1M X 1 FLASH, 27 I/O, PIA-GENERAL PURPOSE, PQCC52 |

| M8813F3Y-90K1T | 1M X 1 FLASH, 27 I/O, PIA-GENERAL PURPOSE, PQCC52 |

| M906-01-125.0000LF | 125 MHz, OTHER CLOCK GENERATOR, CQCC36 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M88141W-15K1T | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:In-System Programmable ISP Multiple-Memory and Logic FLASHPSD Systems with CPLD for MCUs |

| M88141W-15K6T | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:In-System Programmable ISP Multiple-Memory and Logic FLASHPSD Systems with CPLD for MCUs |

| M88141W-15T1T | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:In-System Programmable ISP Multiple-Memory and Logic FLASHPSD Systems with CPLD for MCUs |

| M88141W-15T6T | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:In-System Programmable ISP Multiple-Memory and Logic FLASHPSD Systems with CPLD for MCUs |

| M88141W-90K1T | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:In-System Programmable ISP Multiple-Memory and Logic FLASHPSD Systems with CPLD for MCUs |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。