- 鎮ㄧ従(xi脿n)鍦ㄧ殑浣嶇疆锛�璨疯常IC缍�(w菐ng) > PDF鐩寗4455 > M7A3P1000-1PQG208 (Microsemi SoC)IC FPGA 1KB FLASH 1M 208-PQFP PDF璩囨枡涓嬭級

鍙冩暩(sh霉)璩囨枡

| 鍨嬭櫉(h脿o)锛� | M7A3P1000-1PQG208 |

| 寤犲晢锛� | Microsemi SoC |

| 鏂囦欢闋�(y猫)鏁�(sh霉)锛� | 191/220闋�(y猫) |

| 鏂囦欢澶у皬锛� | 0K |

| 鎻忚堪锛� | IC FPGA 1KB FLASH 1M 208-PQFP |

| 妯�(bi膩o)婧�(zh菙n)鍖呰锛� | 24 |

| 绯诲垪锛� | ProASIC3 |

| RAM 浣嶇附瑷�(j矛)锛� | 147456 |

| 杓稿叆/杓稿嚭鏁�(sh霉)锛� | 154 |

| 闁€鏁�(sh霉)锛� | 1000000 |

| 闆绘簮闆诲锛� | 1.425 V ~ 1.575 V |

| 瀹夎椤炲瀷锛� | 琛ㄩ潰璨艰 |

| 宸ヤ綔婧害锛� | 0°C ~ 70°C |

| 灏佽/澶栨锛� | 208-BFQFP |

| 渚涙噳(y墨ng)鍟嗚ō(sh猫)鍌欏皝瑁濓細 | 208-PQFP锛�28x28锛� |

绗�1闋�(y猫)绗�2闋�(y猫)绗�3闋�(y猫)绗�4闋�(y猫)绗�5闋�(y猫)绗�6闋�(y猫)绗�7闋�(y猫)绗�8闋�(y猫)绗�9闋�(y猫)绗�10闋�(y猫)绗�11闋�(y猫)绗�12闋�(y猫)绗�13闋�(y猫)绗�14闋�(y猫)绗�15闋�(y猫)绗�16闋�(y猫)绗�17闋�(y猫)绗�18闋�(y猫)绗�19闋�(y猫)绗�20闋�(y猫)绗�21闋�(y猫)绗�22闋�(y猫)绗�23闋�(y猫)绗�24闋�(y猫)绗�25闋�(y猫)绗�26闋�(y猫)绗�27闋�(y猫)绗�28闋�(y猫)绗�29闋�(y猫)绗�30闋�(y猫)绗�31闋�(y猫)绗�32闋�(y猫)绗�33闋�(y猫)绗�34闋�(y猫)绗�35闋�(y猫)绗�36闋�(y猫)绗�37闋�(y猫)绗�38闋�(y猫)绗�39闋�(y猫)绗�40闋�(y猫)绗�41闋�(y猫)绗�42闋�(y猫)绗�43闋�(y猫)绗�44闋�(y猫)绗�45闋�(y猫)绗�46闋�(y猫)绗�47闋�(y猫)绗�48闋�(y猫)绗�49闋�(y猫)绗�50闋�(y猫)绗�51闋�(y猫)绗�52闋�(y猫)绗�53闋�(y猫)绗�54闋�(y猫)绗�55闋�(y猫)绗�56闋�(y猫)绗�57闋�(y猫)绗�58闋�(y猫)绗�59闋�(y猫)绗�60闋�(y猫)绗�61闋�(y猫)绗�62闋�(y猫)绗�63闋�(y猫)绗�64闋�(y猫)绗�65闋�(y猫)绗�66闋�(y猫)绗�67闋�(y猫)绗�68闋�(y猫)绗�69闋�(y猫)绗�70闋�(y猫)绗�71闋�(y猫)绗�72闋�(y猫)绗�73闋�(y猫)绗�74闋�(y猫)绗�75闋�(y猫)绗�76闋�(y猫)绗�77闋�(y猫)绗�78闋�(y猫)绗�79闋�(y猫)绗�80闋�(y猫)绗�81闋�(y猫)绗�82闋�(y猫)绗�83闋�(y猫)绗�84闋�(y猫)绗�85闋�(y猫)绗�86闋�(y猫)绗�87闋�(y猫)绗�88闋�(y猫)绗�89闋�(y猫)绗�90闋�(y猫)绗�91闋�(y猫)绗�92闋�(y猫)绗�93闋�(y猫)绗�94闋�(y猫)绗�95闋�(y猫)绗�96闋�(y猫)绗�97闋�(y猫)绗�98闋�(y猫)绗�99闋�(y猫)绗�100闋�(y猫)绗�101闋�(y猫)绗�102闋�(y猫)绗�103闋�(y猫)绗�104闋�(y猫)绗�105闋�(y猫)绗�106闋�(y猫)绗�107闋�(y猫)绗�108闋�(y猫)绗�109闋�(y猫)绗�110闋�(y猫)绗�111闋�(y猫)绗�112闋�(y猫)绗�113闋�(y猫)绗�114闋�(y猫)绗�115闋�(y猫)绗�116闋�(y猫)绗�117闋�(y猫)绗�118闋�(y猫)绗�119闋�(y猫)绗�120闋�(y猫)绗�121闋�(y猫)绗�122闋�(y猫)绗�123闋�(y猫)绗�124闋�(y猫)绗�125闋�(y猫)绗�126闋�(y猫)绗�127闋�(y猫)绗�128闋�(y猫)绗�129闋�(y猫)绗�130闋�(y猫)绗�131闋�(y猫)绗�132闋�(y猫)绗�133闋�(y猫)绗�134闋�(y猫)绗�135闋�(y猫)绗�136闋�(y猫)绗�137闋�(y猫)绗�138闋�(y猫)绗�139闋�(y猫)绗�140闋�(y猫)绗�141闋�(y猫)绗�142闋�(y猫)绗�143闋�(y猫)绗�144闋�(y猫)绗�145闋�(y猫)绗�146闋�(y猫)绗�147闋�(y猫)绗�148闋�(y猫)绗�149闋�(y猫)绗�150闋�(y猫)绗�151闋�(y猫)绗�152闋�(y猫)绗�153闋�(y猫)绗�154闋�(y猫)绗�155闋�(y猫)绗�156闋�(y猫)绗�157闋�(y猫)绗�158闋�(y猫)绗�159闋�(y猫)绗�160闋�(y猫)绗�161闋�(y猫)绗�162闋�(y猫)绗�163闋�(y猫)绗�164闋�(y猫)绗�165闋�(y猫)绗�166闋�(y猫)绗�167闋�(y猫)绗�168闋�(y猫)绗�169闋�(y猫)绗�170闋�(y猫)绗�171闋�(y猫)绗�172闋�(y猫)绗�173闋�(y猫)绗�174闋�(y猫)绗�175闋�(y猫)绗�176闋�(y猫)绗�177闋�(y猫)绗�178闋�(y猫)绗�179闋�(y猫)绗�180闋�(y猫)绗�181闋�(y猫)绗�182闋�(y猫)绗�183闋�(y猫)绗�184闋�(y猫)绗�185闋�(y猫)绗�186闋�(y猫)绗�187闋�(y猫)绗�188闋�(y猫)绗�189闋�(y猫)绗�190闋�(y猫)鐣�(d膩ng)鍓嶇191闋�(y猫)绗�192闋�(y猫)绗�193闋�(y猫)绗�194闋�(y猫)绗�195闋�(y猫)绗�196闋�(y猫)绗�197闋�(y猫)绗�198闋�(y猫)绗�199闋�(y猫)绗�200闋�(y猫)绗�201闋�(y猫)绗�202闋�(y猫)绗�203闋�(y猫)绗�204闋�(y猫)绗�205闋�(y猫)绗�206闋�(y猫)绗�207闋�(y猫)绗�208闋�(y猫)绗�209闋�(y猫)绗�210闋�(y猫)绗�211闋�(y猫)绗�212闋�(y猫)绗�213闋�(y猫)绗�214闋�(y猫)绗�215闋�(y猫)绗�216闋�(y猫)绗�217闋�(y猫)绗�218闋�(y猫)绗�219闋�(y猫)绗�220闋�(y猫)

ProASIC3 DC and Switching Characteristics

2-58

Revision 13

1.5 V LVCMOS (JESD8-11)

Low-Voltage CMOS for 1.5 V is an extension of the LVCMOS standard (JESD8-5) used for general-

purpose 1.5 V applications. It uses a 1.5 V input buffer and a push-pull output buffer.

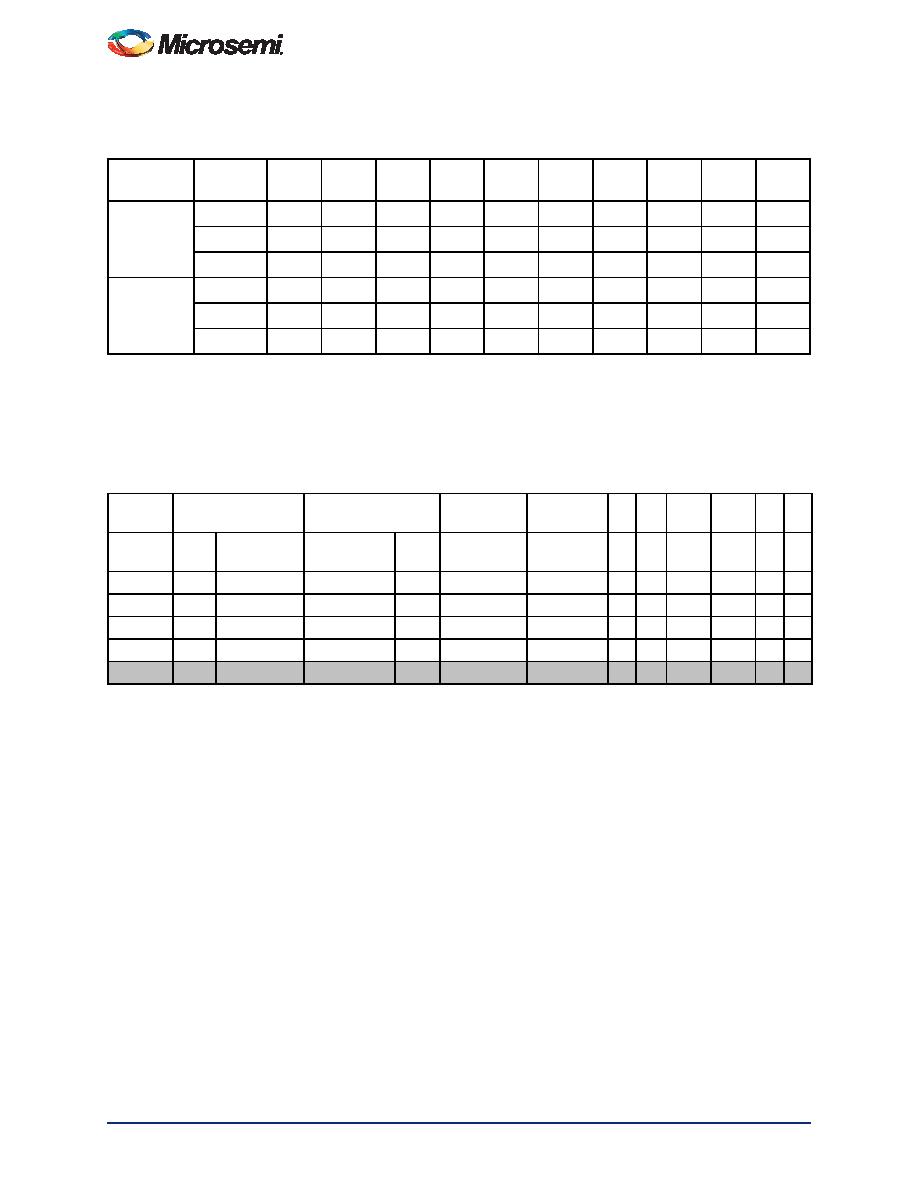

Table 2-75 1.8 V LVCMOS Low Slew

Commercial-Case Conditions: TJ = 70掳C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V

Applicable to Standard I/O Banks

Drive

Strength

Speed

Grade

tDOUT

tDP

tDIN

tPY

tEOUT

tZL

tZH

tLZ

tHZ

Units

2 mA

Std.

0.66

15.01

0.04

1.20

0.43

13.15

15.01

1.99

ns

鈥�1

0.56

12.77

0.04

1.02

0.36

11.19

12.77

1.70

ns

鈥�2

0.49

11.21

0.03

0.90

0.32

9.82

11.21

1.49

ns

4 mA

Std.

0.66

10.10

0.04

1.20

0.43

9.55

10.10

2.41

2.37

ns

鈥�1

0.56

8.59

0.04

1.02

0.36

8.13

8.59

2.05

2.02

ns

鈥�2

0.49

7.54

0.03

0.90

0.32

7.13

7.54

1.80

1.77

ns

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-76 Minimum and Maximum DC Input and Output Levels

Applicable to Advanced I/O Banks

1.5 V

LVCMOS

VIL

VIH

VOL

VOH

IOL IOH IOSL IOSH IIL1 IIH2

Drive

Strength

Min.

V

Max.

V

Min.

V

Max.,

V

Max.

V

Min.

VmA mA

Max.

mA3

Max.

mA3 A4 A4

2 mA

鈥�0.3

0.35 * VCCI

0.65 * VCCI 1.575

0.25 * VCCI 0.75 * VCCI

2

16

13

10 10

4 mA

鈥�0.3

0.35 * VCCI

0.65 * VCCI 1.575

0.25 * VCCI 0.75 * VCCI

4

33

25

10 10

6 mA

鈥�0.3

0.35 * VCCI

0.65 * VCCI 1.575

0.25 * VCCI 0.75 * VCCI 6

6

39

32

10 10

8 mA

鈥�0.3

0.35 * VCCI

0.65 * VCCI 1.575

0.25 * VCCI 0.75 * VCCI 8

8

55

66

10 10

12 mA

鈥�0.3

0.35 * VCCI

0.65 * VCCI 1.575

0.25 * VCCI 0.75 * VCCI 12 12

55

66

10 10

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where 鈥�0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is

larger when operating outside recommended ranges

3. Currents are measured at high temperature (100掳C junction temperature) and maximum voltage.

4. Currents are measured at 85掳C junction temperature.

5. Software default selection highlighted in gray.

鐩搁棞(gu膩n)PDF璩囨枡 |

PDF鎻忚堪 |

|---|---|

| EP4CE40F23I8L | IC CYCLONE IV FPGA 40K 484FBGA |

| 5206478-4 | CONN D-SUB BACKSHELL 37 POS |

| EP4CE40F23I7 | IC CYCLONE IV FPGA 40K 484FBGA |

| EP4CE40F23C6 | IC CYCLONE IV FPGA 40K 484FBGA |

| AMC30DRES-S93 | CONN EDGECARD 60POS .100 EYELET |

鐩搁棞(gu膩n)浠g悊鍟�/鎶€琛�(sh霉)鍙冩暩(sh霉) |

鍙冩暩(sh霉)鎻忚堪 |

|---|---|

| M7A3P1000-1PQG208I | 鍔熻兘鎻忚堪:IC FPGA 1KB FLASH 1M 208-PQFP RoHS:鏄� 椤炲垾:闆嗘垚闆昏矾 (IC) >> 宓屽叆寮� - FPGA锛堢従(xi脿n)鍫�(ch菐ng)鍙法绋嬮杸闄e垪锛� 绯诲垪:ProASIC3 鐢�(ch菐n)鍝佸煿瑷�(x霉n)妯″:Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview 鐗硅壊鐢�(ch菐n)鍝�:Cyclone? IV FPGAs 妯�(bi膩o)婧�(zh菙n)鍖呰:60 绯诲垪:CYCLONE® IV GX LAB/CLB鏁�(sh霉):9360 閭忚集鍏冧欢/鍠厓鏁�(sh霉):149760 RAM 浣嶇附瑷�(j矛):6635520 杓稿叆/杓稿嚭鏁�(sh霉):270 闁€鏁�(sh霉):- 闆绘簮闆诲:1.16 V ~ 1.24 V 瀹夎椤炲瀷:琛ㄩ潰璨艰 宸ヤ綔婧害:0°C ~ 85°C 灏佽/澶栨:484-BGA 渚涙噳(y墨ng)鍟嗚ō(sh猫)鍌欏皝瑁�:484-FBGA锛�23x23锛� |

| M7A3P1000-2FG144 | 鍔熻兘鎻忚堪:IC FPGA 1KB FLASH 1M 144-FBGA RoHS:鍚� 椤炲垾:闆嗘垚闆昏矾 (IC) >> 宓屽叆寮� - FPGA锛堢従(xi脿n)鍫�(ch菐ng)鍙法绋嬮杸闄e垪锛� 绯诲垪:ProASIC3 妯�(bi膩o)婧�(zh菙n)鍖呰:40 绯诲垪:SX-A LAB/CLB鏁�(sh霉):6036 閭忚集鍏冧欢/鍠厓鏁�(sh霉):- RAM 浣嶇附瑷�(j矛):- 杓稿叆/杓稿嚭鏁�(sh霉):360 闁€鏁�(sh霉):108000 闆绘簮闆诲:2.25 V ~ 5.25 V 瀹夎椤炲瀷:琛ㄩ潰璨艰 宸ヤ綔婧害:0°C ~ 70°C 灏佽/澶栨:484-BGA 渚涙噳(y墨ng)鍟嗚ō(sh猫)鍌欏皝瑁�:484-FPBGA锛�27X27锛� |

| M7A3P1000-2FG144I | 鍔熻兘鎻忚堪:IC FPGA 1KB FLASH 1M 144-FBGA RoHS:鍚� 椤炲垾:闆嗘垚闆昏矾 (IC) >> 宓屽叆寮� - FPGA锛堢従(xi脿n)鍫�(ch菐ng)鍙法绋嬮杸闄e垪锛� 绯诲垪:ProASIC3 妯�(bi膩o)婧�(zh菙n)鍖呰:40 绯诲垪:SX-A LAB/CLB鏁�(sh霉):6036 閭忚集鍏冧欢/鍠厓鏁�(sh霉):- RAM 浣嶇附瑷�(j矛):- 杓稿叆/杓稿嚭鏁�(sh霉):360 闁€鏁�(sh霉):108000 闆绘簮闆诲:2.25 V ~ 5.25 V 瀹夎椤炲瀷:琛ㄩ潰璨艰 宸ヤ綔婧害:0°C ~ 70°C 灏佽/澶栨:484-BGA 渚涙噳(y墨ng)鍟嗚ō(sh猫)鍌欏皝瑁�:484-FPBGA锛�27X27锛� |

| M7A3P1000-2FG256 | 鍔熻兘鎻忚堪:IC FPGA 1KB FLASH 1M 256-FBGA RoHS:鍚� 椤炲垾:闆嗘垚闆昏矾 (IC) >> 宓屽叆寮� - FPGA锛堢従(xi脿n)鍫�(ch菐ng)鍙法绋嬮杸闄e垪锛� 绯诲垪:ProASIC3 妯�(bi膩o)婧�(zh菙n)鍖呰:40 绯诲垪:SX-A LAB/CLB鏁�(sh霉):6036 閭忚集鍏冧欢/鍠厓鏁�(sh霉):- RAM 浣嶇附瑷�(j矛):- 杓稿叆/杓稿嚭鏁�(sh霉):360 闁€鏁�(sh霉):108000 闆绘簮闆诲:2.25 V ~ 5.25 V 瀹夎椤炲瀷:琛ㄩ潰璨艰 宸ヤ綔婧害:0°C ~ 70°C 灏佽/澶栨:484-BGA 渚涙噳(y墨ng)鍟嗚ō(sh猫)鍌欏皝瑁�:484-FPBGA锛�27X27锛� |

| M7A3P1000-2FG256I | 鍔熻兘鎻忚堪:IC FPGA 1KB FLASH 1M 256-FBGA RoHS:鍚� 椤炲垾:闆嗘垚闆昏矾 (IC) >> 宓屽叆寮� - FPGA锛堢従(xi脿n)鍫�(ch菐ng)鍙法绋嬮杸闄e垪锛� 绯诲垪:ProASIC3 鐢�(ch菐n)鍝佸煿瑷�(x霉n)妯″:Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview 鐗硅壊鐢�(ch菐n)鍝�:Cyclone? IV FPGAs 妯�(bi膩o)婧�(zh菙n)鍖呰:60 绯诲垪:CYCLONE® IV GX LAB/CLB鏁�(sh霉):9360 閭忚集鍏冧欢/鍠厓鏁�(sh霉):149760 RAM 浣嶇附瑷�(j矛):6635520 杓稿叆/杓稿嚭鏁�(sh霉):270 闁€鏁�(sh霉):- 闆绘簮闆诲:1.16 V ~ 1.24 V 瀹夎椤炲瀷:琛ㄩ潰璨艰 宸ヤ綔婧害:0°C ~ 85°C 灏佽/澶栨:484-BGA 渚涙噳(y墨ng)鍟嗚ō(sh猫)鍌欏皝瑁�:484-FBGA锛�23x23锛� |

鐧�(f膩)甯冪穵鎬ラ噰璩�(g貌u)锛�3鍒嗛悩宸﹀彸鎮ㄥ皣寰楀埌鍥炲京(f霉)銆�