- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370894 > M38197M6-XXXFP (Mitsubishi Electric Corporation) SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER PDF資料下載

參數(shù)資料

| 型號: | M38197M6-XXXFP |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| 中文描述: | 單芯片8位CMOS微機(jī) |

| 文件頁數(shù): | 33/60頁 |

| 文件大小: | 664K |

| 代理商: | M38197M6-XXXFP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁當(dāng)前第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

33

3819 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

MITSUBISHI MICROCOMPUTERS

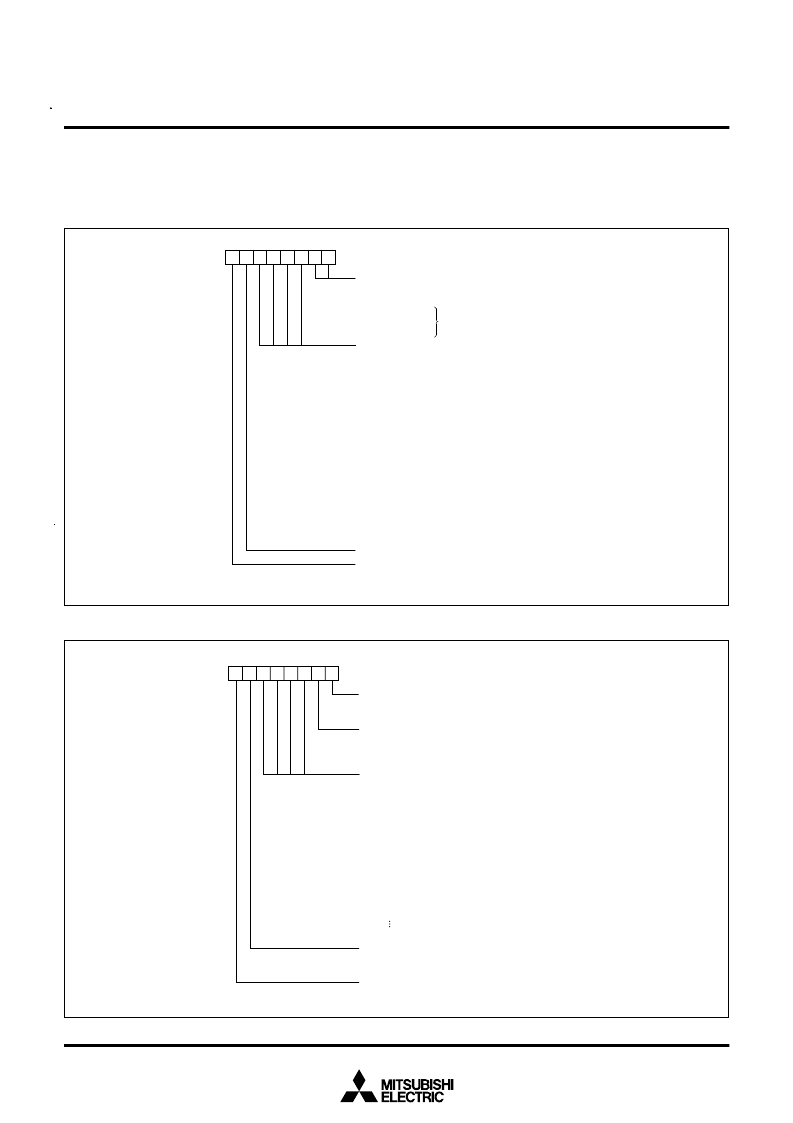

FLDC Mode Registers (FLDM 1, FLDM 2)

0036

16

, 0037

16

The FLDC mode register 1 (address 0036

16

) and FLDC mode reg-

ister 2 (address 0037

16

) are a seven bit register and an eight bit

register respectively which are used to control the FLD automatic

display and set the blanking time T

scan

for key-scan.

Fig. KA-2 Structure of FLDC mode register 1

Fig. KA-3 Structure of FLDC mode register 2

T

scan

control bits

b1

b0

0 0 : 0 FLD digit interrupt (at rising edge of each digit)

0 1 : 1

T

disp

1 0 : 2

T

disp

1 1 : 3

T

disp

T

off

control bits

(Setting of digit/segment OFF time)

b5

b4

b3

b2

0 0 0 0 : 1/16

T

disp

0 0 0 1 : 2/16

T

disp

0 0 1 0 : 3/16

T

disp

0 0 1 1 : 4/16

T

disp

0 1 0 0 : 5/16

T

disp

0 1 0 1 : 6/16

T

disp

0 1 1 0 : 7/16

T

disp

0 1 1 1 : 8/16

T

disp

1 0 0 0 : 9/16

T

disp

1 0 0 1 : 10/16

T

disp

1 0 1 0 : 11/16

T

disp

1 0 1 1 : 12/16

T

disp

1 1 0 0 : 13/16

T

disp

1 1 0 1 : 14/16

T

disp

1 1 1 0 : 15/16

T

disp

1 1 1 1 : 16/16

T

disp

Not used (returns “0” when read)

High-breakdown-voltage drivability selection bit

0 : Strong drivability

1 : Weak drivability

b7

FLDC mode register 1

(FLDM 1 : address 0036

16

)

b0

FLD blanking interrupt

(at falling edge of the last digit)

Automatic display control bit(P0, P1, P2

0

–P2

3

, P3, P8, P9, PA)

0 : Ordinary mode

1 : Automatic display mode

Display start bit

0 : Display stopped

1 : Display in progress

(display starts by writing “1” to this bit which is set to “0”)

T

disp

control bits

(digit time setting, at 8 MHz oscillation frequency)

b5

b4

b3

b2

0 0 0 0 : 128

μ

s

0 0 0 1 : 256

μ

s

0 0 1 0 : 384

μ

s

0 0 1 1 : 512

μ

s

0 1 0 0 : 640

μ

s

0 1 0 1 : 768

μ

s

0 1 1 0 : 896

μ

s

0 1 1 1 : 1024

μ

s

1 0 0 0 : 1152

μ

s

1 0 0 1 : 1280

μ

s

1 0 1 0

1 1 1 1

Pl

0

segment/digit switch bit

0 : Digit

1 : Segment

Pl

1

segment/digit switch bit

0 : Digit

1 : Segment

b7

FLDC mode register 2

(FLDM 2 : address 0037

16

)

b0

Not available

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M38197M9-XXXFP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38197M9-XXXFS | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38197MA-XXXFP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38197MA-XXXFS | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38197MD-XXXFS | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M38197MA127F | 制造商:Panasonic Industrial Company 功能描述:IC |

| M38197MA131F | 制造商:Panasonic Industrial Company 功能描述:IC |

| M38197MA137F | 制造商:Panasonic Industrial Company 功能描述:IC |

| M38197MA161F | 制造商:Panasonic Industrial Company 功能描述:IC |

| M38197MA181F | 制造商:Panasonic Industrial Company 功能描述:IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。