- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98006 > M37534M4-XXXGP 8-BIT, MROM, 6 MHz, MICROCONTROLLER, PQFP32 PDF資料下載

參數(shù)資料

| 型號: | M37534M4-XXXGP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 6 MHz, MICROCONTROLLER, PQFP32 |

| 封裝: | 7 X 7 MM, 0.80 MM PITCH, PLASTIC, LQFP-32 |

| 文件頁數(shù): | 16/58頁 |

| 文件大小: | 753K |

| 代理商: | M37534M4-XXXGP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當(dāng)前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁

7534 Group

Rev.3.00

Oct 23, 2006

page 21 of 53

REJ03B0099-0300

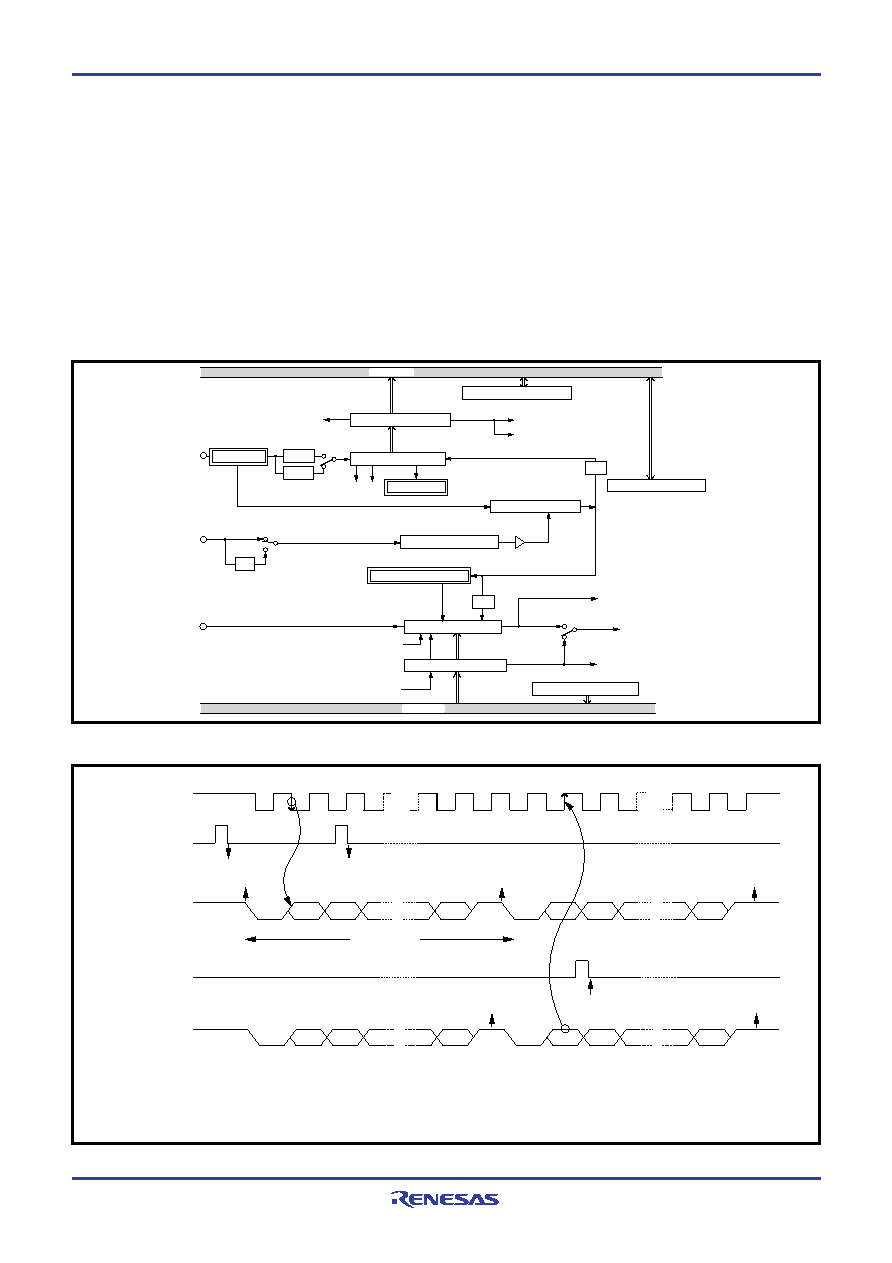

Fig. 22 Block diagram of UART serial I/O

Fig. 23 Operation of UART serial I/O function

Serial Interface

qSerial I/O1

Asynchronous serial I/O (UART) mode

Serial I/O1 can be used as an asynchronous (UART) serial I/O. A

dedicated timer (baud rate generator) is also provided for baud rate

generation when serial I/O1 is in operation.

Eight serial data transfer formats can be selected, and the transfer

formats to be used by a transmitter and a receiver must be identi-

cal.

Each of the transmit and receive shift registers has a buffer register

(the same address on memory). Since the shift register cannot be

written to or read from directly, transmit data is written to the trans-

mit buffer, and receive data is read from the respective buffer regis-

ters. These buffer registers can also hold the next data to be trans-

mitted and receive 2-byte receive data in succession.

By selecting “1” for continuous transmit valid bit (bit 2 of SIO1CON),

continuous transmission of the same data is made possible.

This can be used as a simplified PWM.

OE

PE FE

1/16

XIN

1/4

1/16

Data bus

Receive Buffer Register

Address

(001816)

Receive Shift Register

Receive buffer full flag (RBF)

Receive interrupt request (RI)

ST Detector

SP Detector

UART Control Register

Address (001A16)

Character length selection bit

7-bit

8-bit

Address (001B16)

Clock Control Circuit

Baud Rate Generator

Division ratio 1/(n+1)

Address (001C16)

BRG count source selection bit

Transmit Buffer Register

Data bus

Transmit Shift Register

Address

(001816)

Transmit shift register shift

completion flag (TSC)

Transmit buffer empty flag (TBE)

Transmit interrupt request (TI)

Address (001916)

Character length selection bit

Transmit interrupt source selection bit

Continuous transmit valid bit

Serial I/O1 control register

P10/RXD

P11/TXD

Serial I/O1 status register

ST/SP/PA Generator

TSC=0

TBE=1

RBF=0

TBE=0

RBF=1

ST

D0

D1

SP

D0

D1

ST

SP

TBE=1

TSC=1*

ST

D0

D1

SP

D0

D1

ST

SP

1 : Error flag detection occurs at the same time that the RBF flag becomes “1” (at 1st stop bit, during reception).

2 : The transmit interrupt (TI) can be selected to occur when either the TBE or TSC flag becomes “1”, depending on the setting of the transmit

interrupt source selection bit (TIC) of the serial I/O1 control register.

3 : The receive interrupt (RI) is set when the RBF flag becomes “1”.

4 : After data is written to the transmit buffer when TSC = 1, 0.5 to 1.5 cycles of the data shift cycle is necessary until changing to TSC = 0.

Notes

Transmit/Receive Clock

Transmit Buffer Register

Write Signal

Serial Output TXD

Receive Buffer Register

Read Signal

Serial Input RXD

* Generated at second bit in 2-stop -bit

mode

1 Start Bit

7 or 8 Data Bit

1 or 0 Parity Bit

1 or 2 Stop Bit

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M37534M4-XXXGP | 8-BIT, MROM, 6 MHz, MICROCONTROLLER, PQFP32 |

| M37534E4GP | 8-BIT, OTPROM, 6 MHz, MICROCONTROLLER, PQFP32 |

| M37548G3FP | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO20 |

| M37548G1FP | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO20 |

| M37548G2-XXXFP | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO20 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M37534M4-XXXSP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37534RSS | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37536E8SP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37536M4 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37536M4-XXXSP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。