- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98006 > M37516M4H-XXXKP 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PQFP44 PDF資料下載

參數(shù)資料

| 型號: | M37516M4H-XXXKP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PQFP44 |

| 封裝: | PLASTIC, QFN-44 |

| 文件頁數(shù): | 47/65頁 |

| 文件大小: | 1024K |

| 代理商: | M37516M4H-XXXKP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁當(dāng)前第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁

48

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

MITSUBISHI MICROCOMPUTERS

7516 Group (Spec.H)

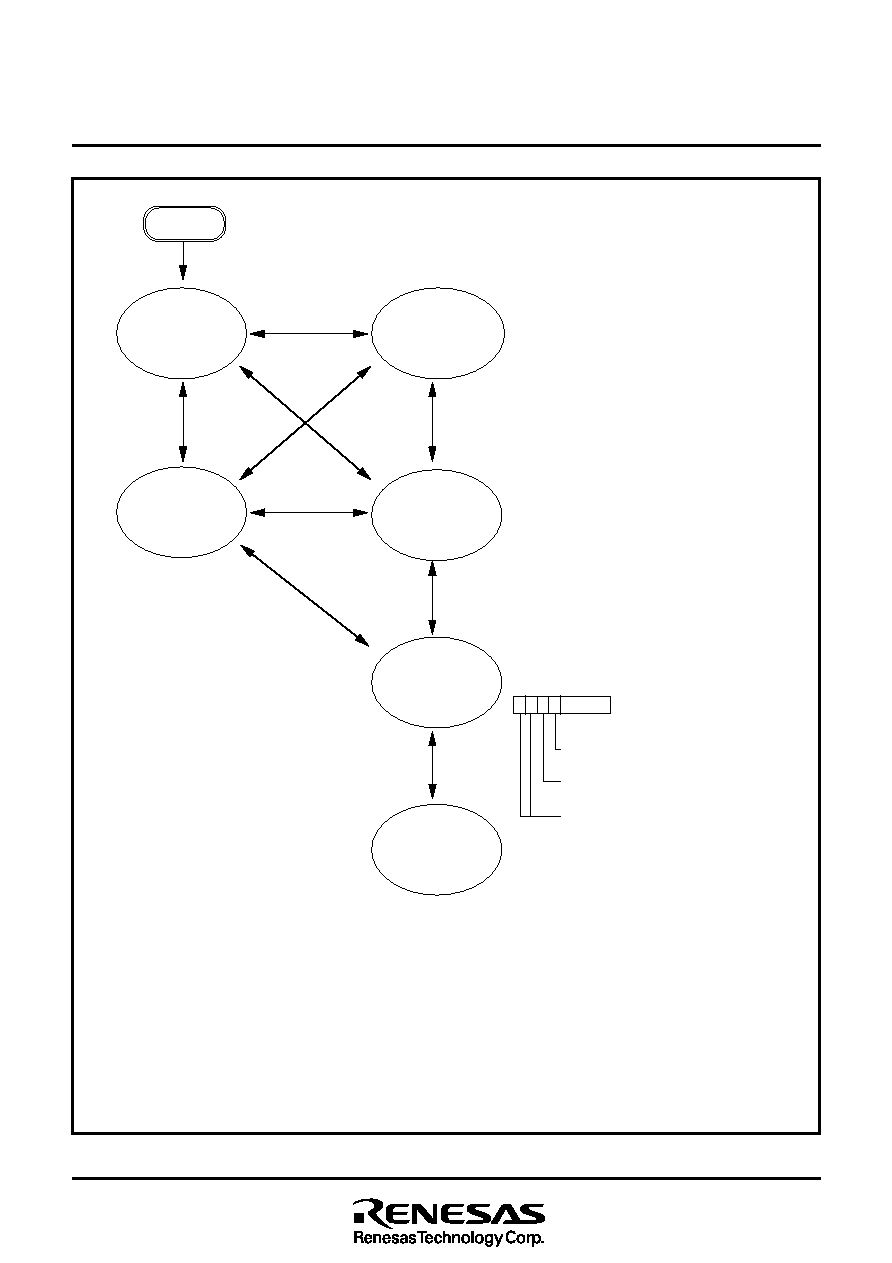

Fig. 56 State transitions of system clock

CM4 : Port Xc switch bit

0 : I/O port function (stop oscillating)

1 : XCIN-XCOUT oscillating function

CM5 : Main clock (XIN- XOUT) stop bit

0 : Operating

1 : Stopped

CM7, CM6: Main clock division ratio selection bits

b7 b6

0

0 :

φ = f(XIN)/2 ( High-speed mode)

0

1 :

φ = f(XIN)/8 (Middle-speed mode)

1

0 :

φ = f(XCIN)/2 (Low-speed mode)

1

1 : Not available

Notes

Reset

C

M

4

“1

”

←→

“0

”

C

M

4

“0

” ←→

“1

”

C

M

6

“1

” ←→

“0

”

C

M

4

“1

” ←→

“0

”

C

M

6

“1

” ←→

“0

”

C

M

7

“1

”

←→

“0

”

C

M

4

“1

”

←→

“0

”

C

M

5

“1

”

←→

“0

”

CM6

“1”

←→ “0”

CM6

“1”

←→ “0”

CPU mode register

b7

b4

CM

7

“0

” ←→

“1

”

CM

6

“1

” ←→

“0

”

(CPUM : address 003B16)

CM7 = 0

CM6 = 1

CM5 = 0 (8 MHz oscillating)

CM4 = 0 (32 kHz stopped)

Middle-speed mode

(f(

φ) = 1 MHz)

CM7 = 0

CM6 = 1

CM5 = 0 (8 MHz oscillating)

CM4 = 1 (32 kHz oscillating)

Middle-speed mode

(f(

φ) = 1 MHz)

CM7 = 0

CM6 = 0

CM5 = 0 (8 MHz oscillating)

CM4 = 0 (32 kHz stopped)

High-speed mode

(f(

φ) = 4 MHz)

CM7 = 1

CM6 = 0

CM5 = 0 (8 MHz oscillating)

CM4 = 1 (32 kHz oscillating)

Low-speed mode

(f(

φ)=16 kHz)

CM7 = 1

CM6 = 0

CM5 = 1 (8 MHz stopped)

CM4 = 1 (32 kHz oscillating)

Low-speed mode

(f(

φ)=16 kHz)

CM7 = 0

CM6 = 0

CM5 = 0 (8 MHz oscillating)

CM4 = 1 (32 kHz oscillating)

High-speed mode

(f(

φ) = 4 MHz)

1 : Switch the mode by the allows shown between the mode blocks. (Do not switch between the modes directly without an allow.)

2 : The all modes can be switched to the stop mode or the wait mode and return to the source mode when the stop mode or the wait mode is

ended.

3 : Timer operates in the wait mode.

4 : When bit 0 of MISRG is “0” and the stop mode is ended, a delay of approximately 1 ms occurs by connecting timer 1 in middle/high-speed

mode.

5 : When bit 0 of MISRG is “0” and the stop mode is ended, the following is performed.

(1) After the clock is restarted, a delay of approximately 250 ms occurs in low-speed mode if Timer 12 count source selection bit is “0”.

(2) After the clock is restarted, a delay of approximately 16 ms occurs in low-speed mode if Timer 12 count source selection bit is “1”.

6 : Wait until oscillation stabilizes after oscillating the main clock XIN before the switching from the low-speed mode to middle/high-speed

mode.

7 : The example assumes that 8 MHz is being applied to the XIN pin and 32 kHz to the XCIN pin.

φ indicates the internal clock.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M37516M6H-XXXKP | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PQFP44 |

| M37532E8FP | 8-BIT, OTPROM, 6 MHz, MICROCONTROLLER, PDSO36 |

| M37532M4-XXXGP | 8-BIT, MROM, 6 MHz, MICROCONTROLLER, PQFP32 |

| M37534M4-XXXFP | 8-BIT, MROM, 6 MHz, MICROCONTROLLER, PDSO36 |

| M37534M4-XXXGP | 8-BIT, MROM, 6 MHz, MICROCONTROLLER, PQFP32 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M37516M4-XXXHP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37516M4-XXXKP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37516M5H-XXXKP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37516M5-XXXHP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37516M5-XXXKP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。