- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384636 > M366S6453ETU-C7A (SAMSUNG SEMICONDUCTOR CO. LTD.) SDRAM Unbuffered Module PDF資料下載

參數(shù)資料

| 型號: | M366S6453ETU-C7A |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | SDRAM Unbuffered Module |

| 中文描述: | 內(nèi)存緩沖模塊 |

| 文件頁數(shù): | 12/26頁 |

| 文件大小: | 486K |

| 代理商: | M366S6453ETU-C7A |

128MB, 256MB, 512MB Unbuffered DIMM

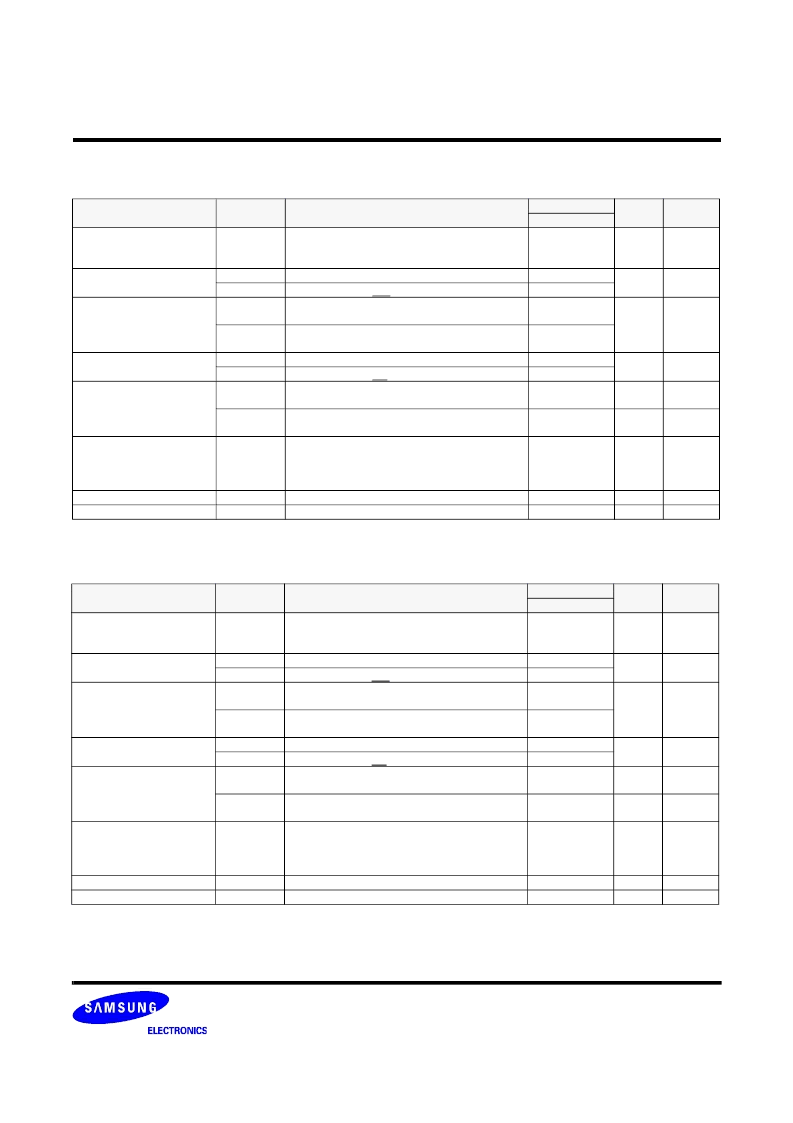

DC CHARACTERISTICS

M366S1654ETS (16M x 64,128MB Module)

Rev. 1.4 May 2004

SDRAM

(Recommended operating condition unless otherwise noted, T

A

= 0 to 70

°

C)

Parameter

Symbol

Test Condition

Version

7A

Unit

Note

Operating current

(One bank active)

I

CC1

Burst length = 1

t

RC

≥

t

RC

(min)

I

O

= 0 mA

CKE

≤

V

IL

(max), t

CC

= 10ns

CKE & CLK

≤

V

IL

(max), t

CC

=

∞

CKE

≥

V

IH

(min), CS

≥

V

IH

(min), t

CC

= 10ns

Input signals are changed one time during 20ns

CKE

≥

V

IH

(min), CLK

≤

V

IL

(max), t

CC

=

∞

Input signals are stable

CKE

≤

V

IL

(max), t

CC

= 10ns

CKE & CLK

≤

V

IL

(max), t

CC

=

∞

CKE

≥

V

IH

(min), CS

≥

V

IH

(min), t

CC

= 10ns

Input signals are changed one time during 20ns

CKE

≥

V

IH

(min), CLK

≤

V

IL

(max), t

CC

=

∞

Input signals are stable

I

O

= 0 mA

Page burst

4Banks activated

t

CCD

= 2CLKs

t

RC

≥

t

RC

(min)

CKE

≤

0.2V

360

mA

1

Precharge standby current

in power-down mode

I

CC2

P

I

CC2

PS

8

8

mA

Precharge standby current

in non power-down mode

I

CC2

N

80

mA

I

CC2

NS

40

Active standby current in

power-down mode

I

CC3

P

I

CC3

PS

25

25

mA

Active standby current in

non power-down mode

(One bank active)

I

CC3

N

100

mA

I

CC3

NS

100

mA

Operating current

(Burst mode)

I

CC4

520

mA

1

Refresh current

Self refresh current

I

CC5

I

CC6

720

12

mA

mA

2

(Recommended operating condition unless otherwise noted, T

A

= 0 to 70

°

C)

Parameter

Symbol

Test Condition

Version

7A

Unit

Note

Operating current

(One bank active)

I

CC1

Burst length = 1

t

RC

≥

t

RC

(min)

I

O

= 0 mA

CKE

≤

V

IL

(max), t

CC

= 10ns

CKE & CLK

≤

V

IL

(max), t

CC

=

∞

CKE

≥

V

IH

(min), CS

≥

V

IH

(min), t

CC

= 10ns

Input signals are changed one time during 20ns

CKE

≥

V

IH

(min), CLK

≤

V

IL

(max), t

CC

=

∞

Input signals are stable

CKE

≤

V

IL

(max), t

CC

= 10ns

CKE & CLK

≤

V

IL

(max), t

CC

=

∞

CKE

≥

V

IH

(min), CS

≥

V

IH

(min), t

CC

= 10ns

Input signals are changed one time during 20ns

CKE

≥

V

IH

(min), CLK

≤

V

IL

(max), t

CC

=

∞

Input signals are stable

I

O

= 0 mA

Page burst

4Banks activated

t

CCD

= 2CLKs

t

RC

≥

t

RC

(min)

CKE

≤

0.2V

640

mA

1

Precharge standby current

in power-down mode

I

CC2

P

I

CC2

PS

16

16

mA

Precharge standby current

in non power-down mode

I

CC2

N

160

mA

I

CC2

NS

80

Active standby current in

power-down mode

I

CC3

P

I

CC3

PS

50

50

mA

Active standby current in

non power-down mode

(One bank active)

I

CC3

N

200

mA

I

CC3

NS

200

mA

Operating current

(Burst mode)

I

CC4

800

mA

1

Refresh current

Self refresh current

I

CC5

I

CC6

1,440

24

mA

mA

2

M366S3253ETS(U) (32M x 64, 256MB Module)

Notes :

1. Measured with outputs open.

2. Refresh period is 64ms.

3. Unless otherwise noted, input swing level is CMOS(V

IH

/V

IL

=V

DDQ

/V

SSQ

)

相關PDF資料 |

PDF描述 |

|---|---|

| M374S3253ETS-C7A | SDRAM Unbuffered Module |

| M374S3253ETU-C7A | SDRAM Unbuffered Module |

| M374S6453ETS-C7A | SDRAM Unbuffered Module |

| M374S6453ETU-C7A | SDRAM Unbuffered Module |

| M366S3253ETU-C7A | SDRAM Unbuffered Module |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| M366S6453HUS | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:SDRAM Product Guide |

| M366S6553BTS-C7A | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:SDRAM Unbuffered Module 168pin Unbuffered Module based on 512Mb B-die 62/72-bit Non ECC/ECC |

| M366TAN | 制造商:MTRONPTI 制造商全稱:MTRONPTI 功能描述:5x7 mm, 3.3 Volt, HCMOS/TTL, Surface Mount Oscillator |

| M366TCN | 制造商:MTRONPTI 制造商全稱:MTRONPTI 功能描述:5x7 mm, 3.3 Volt, HCMOS/TTL, Surface Mount Oscillator |

| M3675R-H100C | 制造商:Bonitron 功能描述:OVERVOLTAGE BRAKING RESISTOR |

發(fā)布緊急采購,3分鐘左右您將得到回復。