- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄370832 > M30240SA (Mitsubishi Electric Corporation) SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER PDF資料下載

參數(shù)資料

| 型號(hào): | M30240SA |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| 中文描述: | 單片16位CMOS微機(jī) |

| 文件頁(yè)數(shù): | 59/142頁(yè) |

| 文件大小: | 1637K |

| 代理商: | M30240SA |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)當(dāng)前第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)

1-59

Mitsubishi microcomputers

M30240 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Preliminary Specifications REV. E

Specifications in this manual are tentative and subject to change

Universal Serial Bus

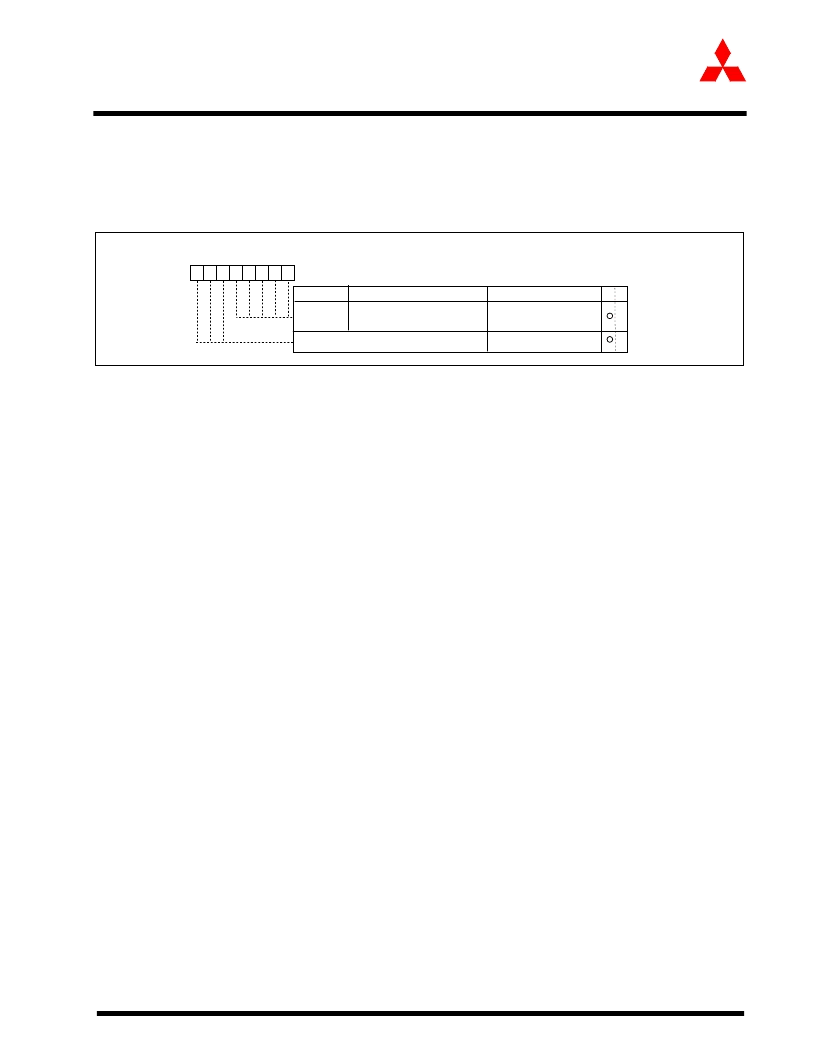

2.18.4.14 USB Endpoint 0 OUT WRT CNT Register

The USB Endpoint 0 OUT WRT CNT Register, shown in Figure 1.46, contains the number of bytes of the cur-

rent data set in the OUT FIFO. The USB FCU sets the value in the Write Count Register after having success-

fully received a packet of data from the host. The CPU reads the register to determine the number of bytes to

be read from the FIFO.

Figure 1.46: USB Endpoint 0 OUT WRT CNT

2.18.4.15 USB Endpoint x IN CSR (Control & Status Register)

The USB Endpoint x IN CSR (Control and Status Register), shown in Figure 1.47, contains control and status

information of the respective IN endpoint 1-4.

INxCSR0 (IN_PKT_RDY) and INxCSR5 (TX_FIFO_NOT_EMPTY):

These two bits are for IN FIFO status when in read operation (see “IN (Transmit) FIFO” operation for details).

The CPU writes a “1” to the INxCSR0 bit to inform the USB FCU that a packet of data is written to the FIFO.

The USB FCU updates the pointers up on this bit set. The USB FCU also updates the pointers upon a packet

of data successfully sent to the host. When the pointer updates are completed, the IN FIFO status is shown

on INxCSR0 and INxCSR5 bits for the CPU to read. The CPU must allow at least one wait state between writ-

ing and reading these bits for proper FIFO status.

INxCSR1 (UNDER_RUN):

This bit is used in ISO mode only to indicate to the CPU that a FIFO underrun has occurred. The USB FCU

sets this bit to a “1” at the beginning of an IN token if no data packet is in the FIFO. Setting this bit causes the

INST12 bit of the Interrupt Status Register 2 to set. The CPU writes a “0” to clear this bit.

INxCSR2 (SEND_STALL):

The CPU writes a “1” to this bit when the endpoint is stalled (transmitter halt). The USB FCU returns a STALL

handshake while this bit is set. The CPU writes a “0” to clear this bit.

INxCSR3 (ISO/TOGGLE_INIT):

When the endpoint is used for isochronous data transfer, the CPU sets this bit to a “1” for the entire duration

of the isochronous transfer. With the ISO bit set to a “1”, the device uses DATA0 as the pid for all packets sent

back to the host.

When the endpoint is required to initialize the data toggle, this set/reset of the TOGGLE_INIT bit method as-

sumes that there is no activity IN transaction to the respective endpoint on the bus at the time the initialization

process is ongoing. Set/reset of the TOGGLE_INIT bit is performed only when an endpoint experiences a con-

figuration event.

INxCSR4 (INTPT):

The CPU writes a “1” to this bit to initialize this endpoint as a status change endpoint for IN transactions. This

bit is set only when the corresponding endpoint is to be used to communicate rate feedback information (see

Chapter. IN (Transmit) FIFOs for details).

INxCSR5 (TX_FIFO_NOT_EMPTY):

The USBFCU sets this bit to a “1” when there is at least one data packet in the IN FIFO. This bit, in conjunction

with IN_PKT_RDY bit, provides the transmit IN FIFO status information (see “IN (Transmit) FIFO” for details).

INxCSR6 (FLUSH):

USB Endpoint 0 OUT Write Count Register

Symbol

EP0WC

Address

0315

16

When reset

00

16

Bit name

Bit symbol

b7

0 0 0

b6

b5

b4

b3

b2

b1

b0

W_CNT0 to

W_CNT4

Function

W

R

Receive byte count

Reserved

Must always be set to "0"

X

X

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M30240SA-XXXFP | SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M30240SC | SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M30240SC-XXXFP | SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M30240ECFP | SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M30240F1 | SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M30240SA-XXXFP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M30240SC | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M30240SC-XXXFP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M30245 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M30245_06 | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:RENESAS 16-BIT SINGLE-CHIP MICROCOMPUTER M16C FAMILY / M16C/20 SERIES |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。