- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45010 > M30100M3-XXXFP 16-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP32 PDF資料下載

參數(shù)資料

| 型號(hào): | M30100M3-XXXFP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 16-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP32 |

| 封裝: | PLASTIC, LQFP-32 |

| 文件頁(yè)數(shù): | 73/163頁(yè) |

| 文件大?。?/td> | 2767K |

| 代理商: | M30100M3-XXXFP |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)當(dāng)前第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)

Under

development

Tentative Specifications REV.E1

Specifications in this manual are tentative and subject to change.

Mitsubishi microcomputers

M30100/M30102 Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

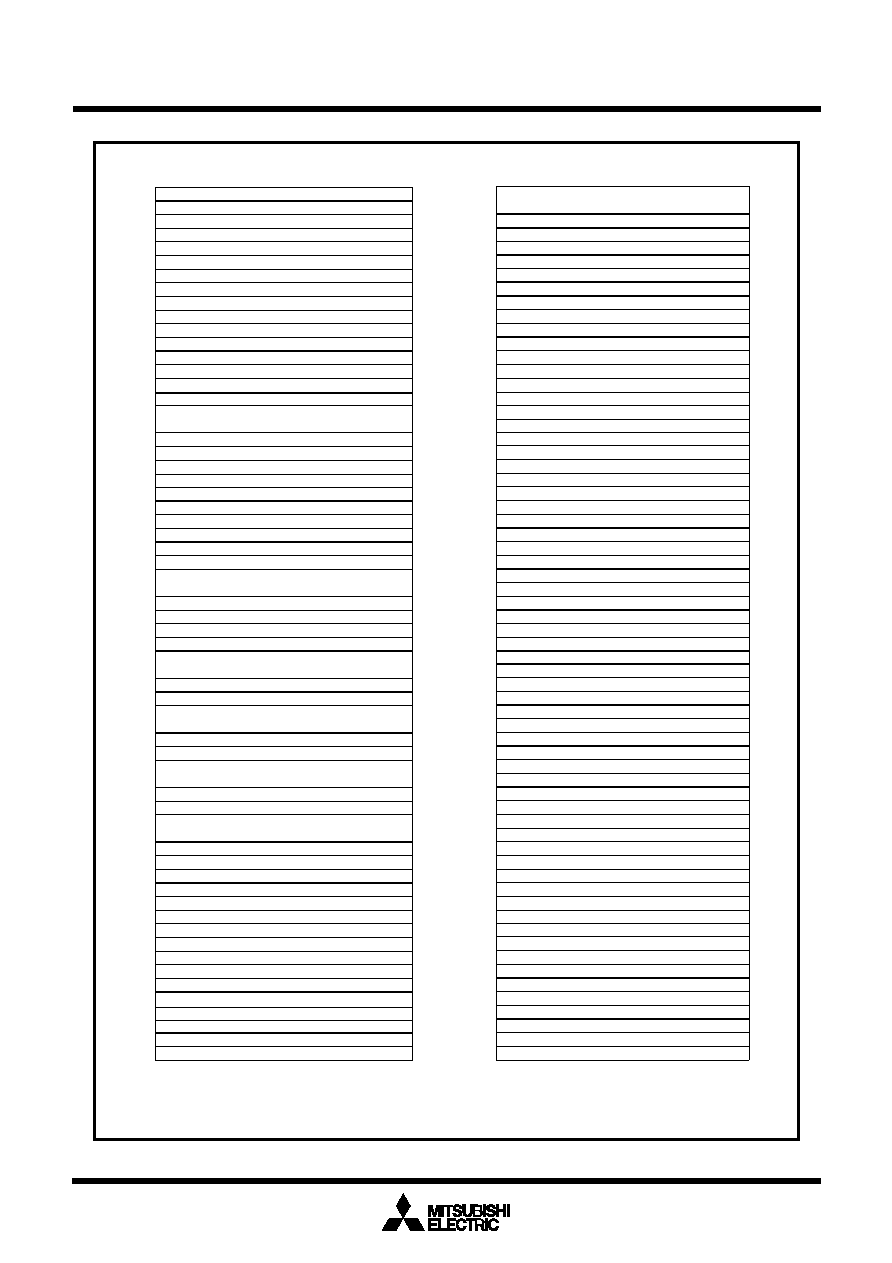

SFR

17

008016

008116

008216

008316

008416

008516

008616

008716

008816

008916

008A16

008B16

008C16

008D16

008E16

008F16

009016

009116

009216

009316

009416

009516

009616

009716

009816

009916

009A16

009B16

009C16

009D16

009E16

009F16

00A016

00A116

00A216

00A316

00A416

00A516

00A616

00A716

00A816

00A916

00AA16

00AB16

00AC16

00AD16

00AE16

00AF16

00B016

00B116

00B216

00B316

00B416

00B516

00B616

00B716

00B816

00B916

00BA16

00BB16

00BC16

00BD16

00BE16

00BF16

Timer Y, Z mode register (TYZMR)

Timer Y secondary (TYSC)

External input enable register (INTEN)

Key input enable register (KIEN)

Timer C control register 1 (TCC1)

Time measurement register (TM)

Timer Y, Z waveform output control register (PUM)

Timer C control register 0 (TCC0)

Timer Y primary (TYPR)

Prescaler Y (PREY)

UART0 transmit/receive mode register (U0MR)

UART0 transmit buffer register (U0TB)

UART0 receive buffer register (U0RB)

UART1 transmit/receive mode register (U1MR)

UART1 transmit buffer register (U1TB)

UART1 receive buffer register (U1RB)

UART0 bit rate generator (U0BRG)

UART0 transmit/receive control register 0 (U0C0)

UART0 transmit/receive control register 1 (U0C1)

UART1 bit rate generator (U1BRG)

UART1 transmit/receive control register 0 (U1C0)

UART1 transmit/receive control register 1 (U1C1)

UART transmit/receive control register 2 (UCON)

Timer Z secondary (TZSC)

Timer Z primary (TZPR)

Prescaler Z (PREZ)

Timer X mode register (TXMR)

Timer X (TX)

Timer count source set register (TCSS)

Prescaler X (PREX)

Timer Y, Z output control register (TYZOC)

Prescaler 1 (PRE1)

Timer 1 (T1)

Timer C counter (TC)

Clock prescaler reset flag (CPSRF)

00C016

00C116

00C216

00C316

00C416

00C516

00C616

00C716

00C816

00C916

00CA16

00CB16

00CC16

00CD16

00CE16

00CF16

00D016

00D116

00D216

00D316

00D416

00D516

00D616

00D716

00D816

00D916

00DA16

00DB16

00DC16

00DD16

00DE16

00DF16

00E016

00E116

00E216

00E316

00E416

00E516

00E616

00E716

00E816

00E916

00EA16

00EB16

00EC16

00ED16

00EE16

00EF16

00F016

00F116

00F216

00F316

00F416

00F516

00F616

00F716

00F816

00F916

00FA16

00FB16

00FC16

00FD16

00FE16

00FF16

A-D register (AD)

Port P0 (P0)

Port P0 direction register (PD0)

Port P1 (P1)

Port P1 direction register (PD1)

Port P2 (P2)

Port P2 direction register (PD2)

Port P3 (P3)

Port P3 direction register (PD3)

Port P4 (P4)

Port P4 direction register (PD4)

Pull-up control register 0 (PUR0)

Pull-up control register 1 (PUR1)

Port P1 drive capacity control register (DRR)

A-D control register 0 (ADCON0)

A-D control register 1 (ADCON1)

A-D control register 2 (ADCON2)

D-A register (DA)

D-A control register (DACON)

Figure 1.6.2. Location of peripheral unit control registers (2)

Note: The blank area is reserved and must not be read or written.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M30100F3TFP | 16-BIT, FLASH, 16 MHz, MICROCONTROLLER, PQFP32 |

| M30102M2T-XXXFP | 16-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP48 |

| M30100M2T-XXXFP | 16-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP32 |

| M30102M6T-XXXFP | 16-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP48 |

| M30102M3-XXXFP | 16-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP48 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M30100T3-RPD-E | 制造商:Renesas Electronics Corporation 功能描述:DEV EMULATOR POD M16C/10 SERIES - Bulk |

| M30100T-PTC | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:Converter for Connecting 32-pin 0.8mm-pitch QFP for M30100T-PRB (for M16C/10 Group M30100) |

| M30-1010046 | 功能描述:集管和線殼 1.25MM FEMALE CRIMP TIN PK OF 105 RoHS:否 產(chǎn)品種類:1.0MM Rectangular Connectors 產(chǎn)品類型:Headers - Pin Strip 系列:DF50 觸點(diǎn)類型:Pin (Male) 節(jié)距:1 mm 位置/觸點(diǎn)數(shù)量:16 排數(shù):1 安裝風(fēng)格:SMD/SMT 安裝角:Right 端接類型:Solder 外殼材料:Liquid Crystal Polymer (LCP) 觸點(diǎn)材料:Brass 觸點(diǎn)電鍍:Gold 制造商:Hirose Connector |

| M3010102636207.32LLZZ | 制造商:3M Electronic Products Division 功能描述:QUOTE # V05-0068 |

| M30102 | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。