- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄370829 > M2V64S30BTP-6 (Mitsubishi Electric Corporation) 64M bit Synchronous DRAM PDF資料下載

參數(shù)資料

| 型號(hào): | M2V64S30BTP-6 |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | 64M bit Synchronous DRAM |

| 中文描述: | 6400位同步DRAM |

| 文件頁(yè)數(shù): | 29/52頁(yè) |

| 文件大小: | 674K |

| 代理商: | M2V64S30BTP-6 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)當(dāng)前第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)

Apr. '99

MITSUBISHI LSIs

MITSUBISHI ELECTRIC

SDRAM (Rev.1.2)

M2V64S20BTP-7,-7L,-8,-8L,-8A,-10,-10L (4-BANK x 4194304-WORD x 4-BIT)

M2V64S30BTP-7,-7L,-8,-8L,-8A,-10,-10L (4-BANK x 2097152-WORD x 8-BIT)

M2V64S40BTP-7,-7L,-8,-8L,-8A,-10,-10L (4-BANK x 1048576-WORD x 16-BIT)

64M bit Synchronous DRAM

29

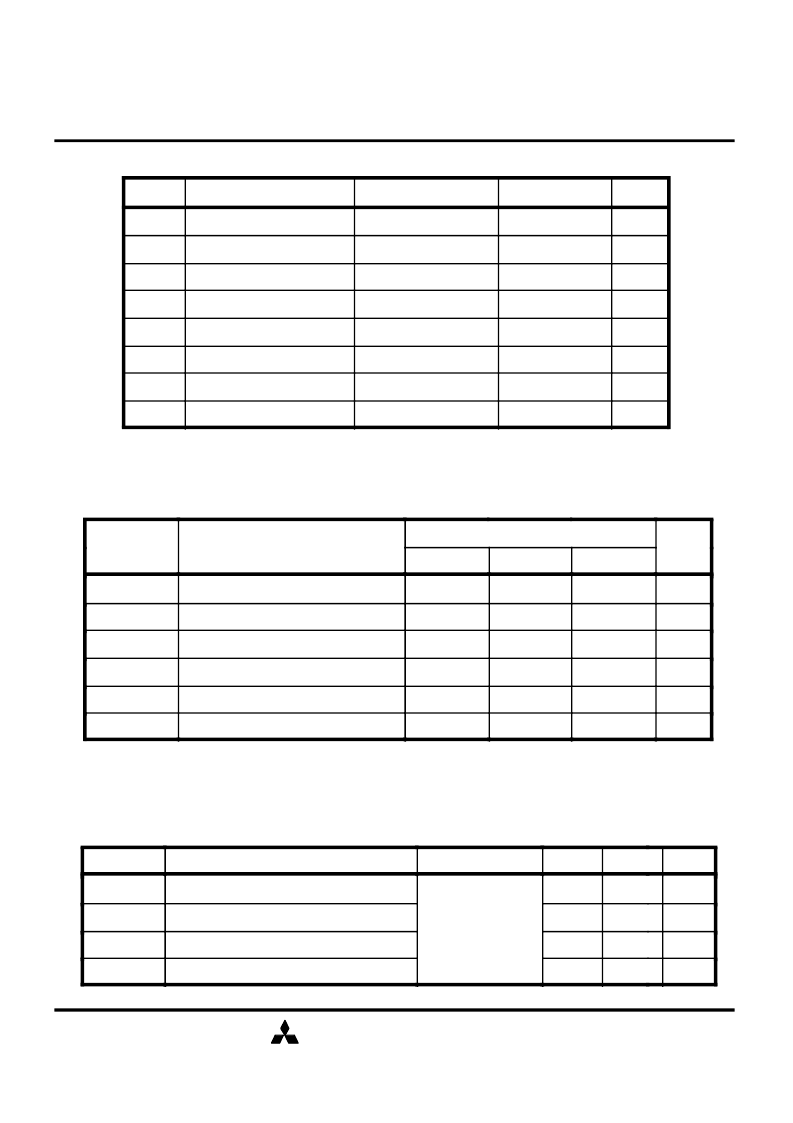

ABSOLUTE MAXIMUM RATINGS

RECOMMENDED OPERATING CONDITIONS

(Ta=0 ~ 70'C, unless otherwise noted)

CAPACITANCE

(Ta=0 ~ 70'C, Vdd = VddQ = 3.3 ± 0.3v, Vss = VssQ = 0v, unless otherwise noted)

Symbol

Parameter

Conditions

Ratings

Unit

Vdd

Supply Voltage

with respect to Vss

-0.5 ~ 4.6

V

VddQ

Supply Voltage for Output

with respect to VssQ

-0.5 ~ 4.6

V

VI

Input Voltage

with respect to Vss

-0.5 ~ Vdd+0.5

V

VO

Output Voltage

with respect to VssQ

-0.5 ~ VddQ+0.5

V

IO

Output Current

50

mA

Pd

Power Dissipation

Ta = 25 'C

1000

mW

Topr

Operating Temperature

0 ~ 70

'C

Tstg

Storage Temperature

-65 ~ 150

'C

Symbol

Parameter

Limits

Unit

Min.

Typ.

Max.

Vdd

Supply Voltage

3.0

3.3

3.6

V

Vss

Supply Voltage

0

0

0

V

VddQ

Supply Voltage for Output

3.0

3.3

3.6

V

VssQ

Supply Voltage for Output

0

0

0

V

VIH

High-Level Input Voltage all inputs

2.0

Vdd+0.3

V

VIL

Low-Level Input Voltage all inputs

-0.3

0.8

V

Note:*

VIH (max) = Vdd+2.0V AC for pulse width<=3ns acceptable.

VIL(min) = -2V AC for pulse width<=3ns acceptable.

Symbol

Parameter

Test Condition

max.

Unit

CI(A)

Input Capacitance, address pin

VI=Vss

5

pF

CI(C)

Input Capacitance, control pin

f=1MHz

5

pF

CI(K)

Input Capacitance, CLK pin

Vi=25mVrms

4

pF

CI/O

Input Capacitance, I/O pin

6.5

pF

min.

2.5

2.5

2.5

4

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M2V64S30BTP-7 | 64M bit Synchronous DRAM |

| M2V64S30BTP-7L | 64M bit Synchronous DRAM |

| M2V64S30BTP-8 | 64M bit Synchronous DRAM |

| M2V64S30BTP-8A | 64M bit Synchronous DRAM |

| M2V64S30BTP-8L | 64M bit Synchronous DRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M2V64S30BTP-7 | 制造商:MITSUBISHI 制造商全稱(chēng):Mitsubishi Electric Semiconductor 功能描述:64M bit Synchronous DRAM |

| M2V64S30BTP-7L | 制造商:MITSUBISHI 制造商全稱(chēng):Mitsubishi Electric Semiconductor 功能描述:64M bit Synchronous DRAM |

| M2V64S30BTP-8 | 制造商:MITSUBISHI 制造商全稱(chēng):Mitsubishi Electric Semiconductor 功能描述:64M bit Synchronous DRAM |

| M2V64S30BTP-8A | 制造商:MITSUBISHI 制造商全稱(chēng):Mitsubishi Electric Semiconductor 功能描述:64M bit Synchronous DRAM |

| M2V64S30BTP-8L | 制造商:MITSUBISHI 制造商全稱(chēng):Mitsubishi Electric Semiconductor 功能描述:64M bit Synchronous DRAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。