- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄296347 > M24256-BFMB6TG/K (STMICROELECTRONICS) 32K X 8 I2C/2-WIRE SERIAL EEPROM, PDSO8 PDF資料下載

參數(shù)資料

| 型號(hào): | M24256-BFMB6TG/K |

| 廠商: | STMICROELECTRONICS |

| 元件分類: | PROM |

| 英文描述: | 32K X 8 I2C/2-WIRE SERIAL EEPROM, PDSO8 |

| 封裝: | 2 X 3 MM, ROHS COMPLIANT, UFDFPN-8 |

| 文件頁數(shù): | 22/42頁 |

| 文件大小: | 501K |

| 代理商: | M24256-BFMB6TG/K |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當(dāng)前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁

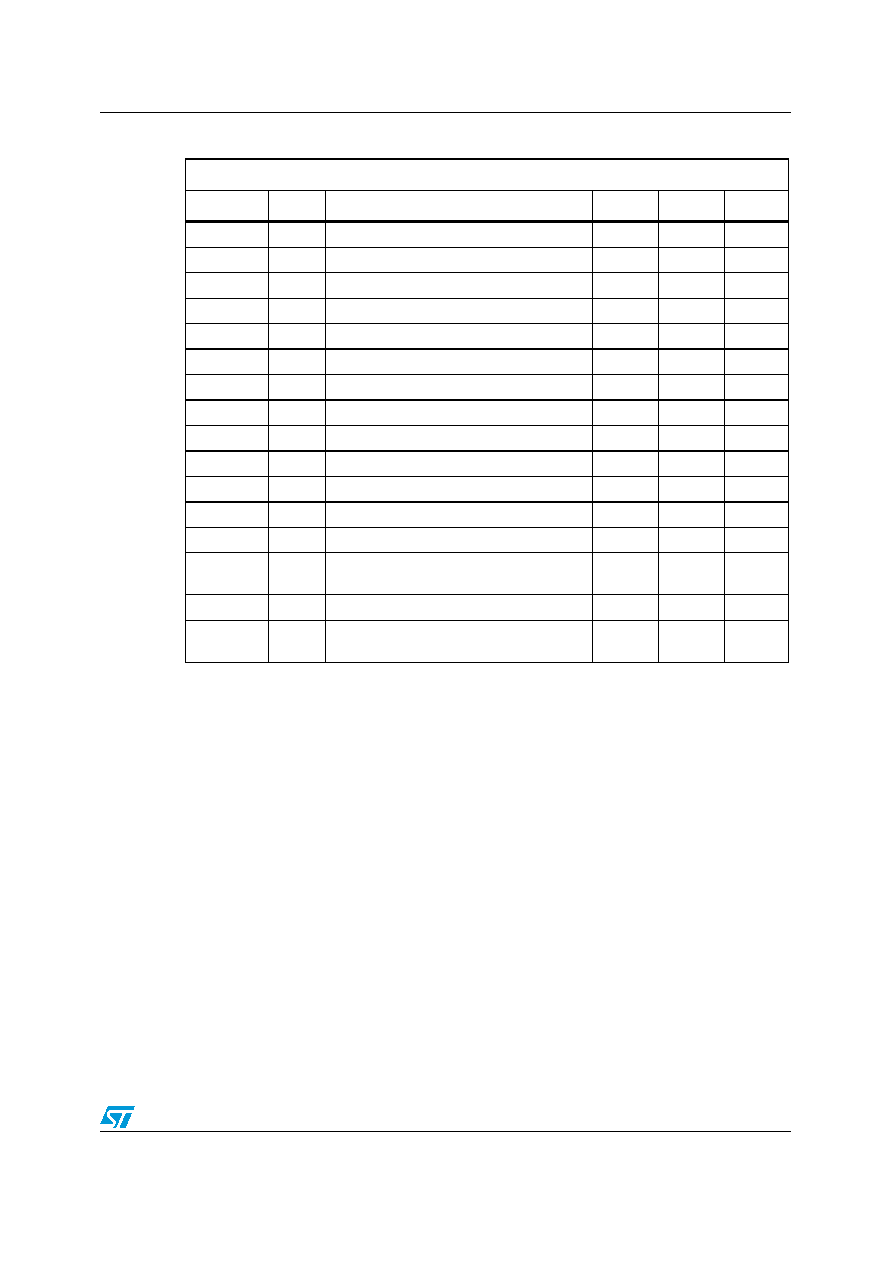

M24256-BF, M24256-BR, M24256-BW, M24256-DR

DC and AC parameters

Doc ID 6757 Rev 21

Table 17.

1 MHz AC characteristics(1)

1.

Only new M24256-BR and M24256-DR devices identified by the process letter K are qualified at 1 MHz.

Symbol

Alt.

Parameter

Min.(2)

2.

All values are referred to VIL(max) and VIH(min).

Unit

fC

fSCL

Clock frequency

0

1

MHz

tCHCL

tHIGH

Clock pulse width high

300

-

ns

tCLCH

tLOW

Clock pulse width low

400

-

ns

tXH1XH2

tR

Input signal rise time

(3)

3.

There is no min. or max. values for the input signal rise and fall times. It is however recommended by the

IC specification that the input signal rise and fall times be more than 20 ns and less than 300 ns when

fC < 400 kHz, or less than 120 ns when fC <1MHz.

ns

tXL1XL2

tF

Input signal fall time

ns

tQL1QL2

(4)

4.

Characterized only, not tested in production.

tF

SDA (out) fall time

20(5)

5.

With CL = 10 pF.

120

ns

tDXCX

tSU:DAT

Data in setup time

80

-

ns

tCLDX

tHD:DAT Data in hold time

0

-

ns

tCLQX

tDH

Data out hold time

50(6)

6.

The new M24xxx devices (identified by the process letter K) offer tCLQX=100 ns (min) and tCLQV=100 ns

(min) which is an improved value compared to the tCLQX=50 ns (min) and tCLQV=50 ns (min) offered by the

current M24xxx devices (identified with the Process letter A)

-ns

tCLQV

(7)(8)

7.

To avoid spurious Start and Stop conditions, a minimum delay is placed between SCL=1 and the falling or

rising edge of SDA.

8.

tCLQV is the time (from the falling edge of SCL) required by the SDA bus line to reach either 0.3VCC or

tAA

Clock low to next data valid (access time)

50(6)

500

ns

tCHDL

tSU:STA

Start condition setup time

250

-

ns

tDLCL

tHD:STA Start condition hold time

250

-

ns

tCHDH

tSU:STO Stop condition setup time

250

-

ns

tDHDL

tBUF

Time between Stop condition and next

Start condition

500

-

ns

tW

tWR

Write time

-

5

ms

tNS

Pulse width ignored (input filter on SCL and

SDA)

-50(9)

9.

The new M24xxx devices (identified with the process letter K) offer tNS = 80 ns (min) which is an improved

value compared to the current M24xxx devices (identified by the process letter A).

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M24308/4-260 | 15 CONTACT(S), MALE, D SUBMINIATURE CONNECTOR |

| M24308/4-2 | 15 CONTACT(S), MALE, D SUBMINIATURE CONNECTOR |

| M24308/4-303 | 15 CONTACT(S), MALE, D SUBMINIATURE CONNECTOR |

| M24308/4-325 | 15 CONTACT(S), MALE, D SUBMINIATURE CONNECTOR |

| M24308/4-261 | 25 CONTACT(S), MALE, D SUBMINIATURE CONNECTOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M24256-BFMC6TG | 功能描述:電可擦除可編程只讀存儲(chǔ)器 256kB Serial I2C 3-Chip Enable 1 MHz RoHS:否 制造商:Atmel 存儲(chǔ)容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時(shí)鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| M24256-BHR | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:512 Kbit and 256 Kbit serial IC bus EEPROM with three Chip Enable lines |

| M24256-BHRDW6TP | 功能描述:電可擦除可編程只讀存儲(chǔ)器 512 Kbit/256 Kbit serial 電可擦除可編程只讀存儲(chǔ)器 RoHS:否 制造商:Atmel 存儲(chǔ)容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時(shí)鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| M24256-BHRMN6P | 功能描述:電可擦除可編程只讀存儲(chǔ)器 512Kbit and 256Kbit bus 電可擦除可編程只讀存儲(chǔ)器 RoHS:否 制造商:Atmel 存儲(chǔ)容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時(shí)鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| M24256-BHRMN6TP | 功能描述:電可擦除可編程只讀存儲(chǔ)器 513 Kbit/256 Kbit serial 電可擦除可編程只讀存儲(chǔ)器 RoHS:否 制造商:Atmel 存儲(chǔ)容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時(shí)鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。