- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄384604 > LMX2485E (NATIONAL SEMICONDUCTOR CORP) 50 MHz - 3.0 GHz High Performance Delta-Sigma Low Power Dual PLLatinum⑩ Frequency Synthesizers with 800 MHz Integer PLL PDF資料下載

參數(shù)資料

| 型號(hào): | LMX2485E |

| 廠(chǎng)商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分類(lèi): | XO, clock |

| 英文描述: | 50 MHz - 3.0 GHz High Performance Delta-Sigma Low Power Dual PLLatinum⑩ Frequency Synthesizers with 800 MHz Integer PLL |

| 中文描述: | PLL FREQUENCY SYNTHESIZER, 3000 MHz, PQCC24 |

| 封裝: | 4 X 4 MM, 0.8 MM, PLASTIC, LLP-24 |

| 文件頁(yè)數(shù): | 29/37頁(yè) |

| 文件大小: | 861K |

| 代理商: | LMX2485E |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)當(dāng)前第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)

Programming Description

(Continued)

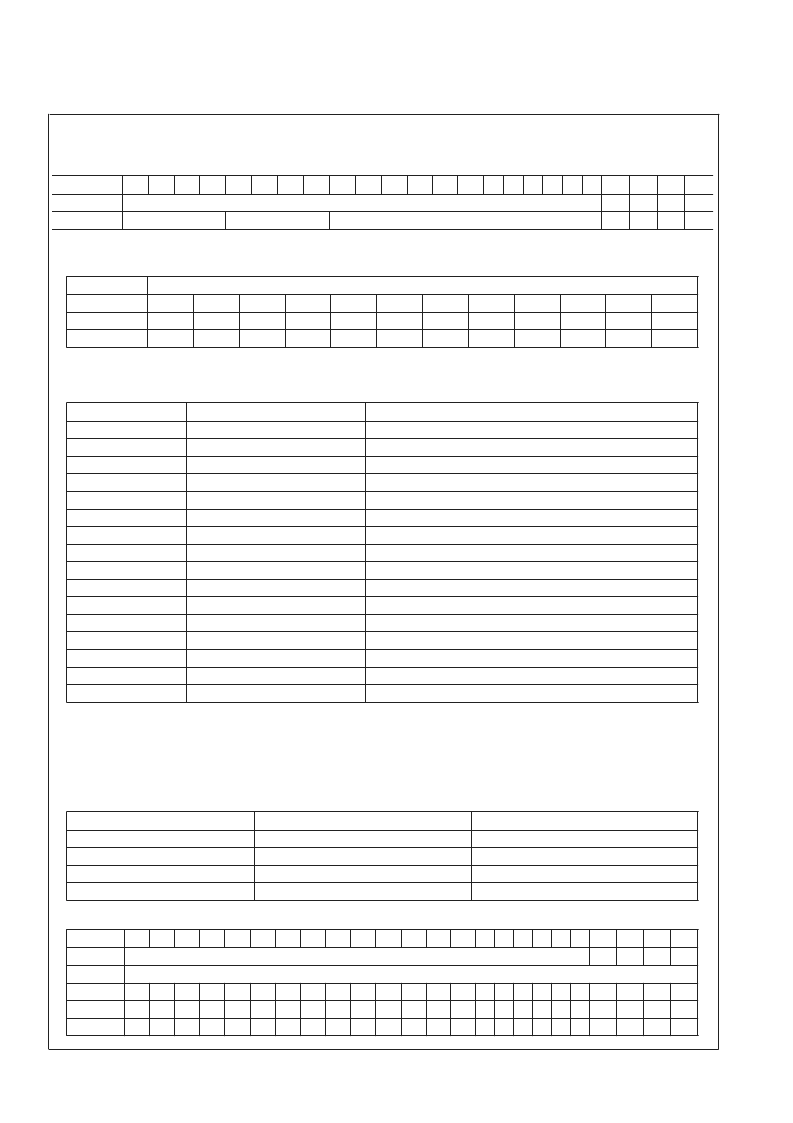

2.4 R3 REGISTER

REGISTER

23

22

21

20

19

18

17

16

15

DATA[19:0]

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

C3

0

C2

1

C1

1

C0

1

R3

ACCESS[3:0]

RF_CPG[3:0]

IF_R[11:0]

2.4.1 IF_R[11:0] -- IF R Divider Value

For the IF R divider, the R value is determined by the IF_R[11:0] bits in the R3 register. The minimum value for IF_R is 3.

R Value

3

...

4095

IF_R[11:0]

0

.

1

0

.

1

0

.

1

0

.

1

0

.

1

0

.

1

0

.

1

0

.

1

0

.

1

0

.

1

1

.

1

1

.

1

2.4.2 RF_CPG -- RF PLL Charge Pump Gain

This is used to control the magnitude of the RF PLL charge pump in steady state operation.

RF_CPG

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Charge Pump State

1X

2X

3X

4X

5X

6X

7X

8X

9X

10X

11X

12X

13X

14X

15X

16X

Typical RF Charge Pump Current at 3 Volts (μA)

95

190

285

380

475

570

665

760

855

950

1045

1140

1235

1330

1425

1520

2.4.3 ACCESS -- Register Access word

It is mandatory that the first 5 registers R0-R4 be programmed. The programming of registers R5-R7 is optional. The

ACCESS[3:0] bits determine which additional registers need to be programmed. Any one of these registers can be individually

programmed. According to the table below, when the state of a register is in default mode, all the bits in that register are forced

to a default state and it is not necessary to program this register. When the register is programmable, it needs to be programmed

through the MICROWIRE. Using this register access technique, the programming required is reduced up to 37%.

ACCESS Bit

ACCESS[0]

ACCESS[1]

ACCESS[2]

ACCESS[3]

Register Location

R3[20]

R3[21]

R3[22]

R3[23]

Register Controlled

Must be set to 1

R5

R6

R7

The default conditions the registers is shown below:

Register

23

22

21

20

19

18

17

16

15

Data[19:0]

R4 Must be programmed manually.

0

0

0

0

0

0

0

0

0

0

0

0

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

C3

C2

C1

C0

R4

R5

R6

R7

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

0

1

1

1

0

1

1

1

1

L

www.national.com

29

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LMX2485ESQ | 50 MHz - 3.0 GHz High Performance Delta-Sigma Low Power Dual PLLatinum⑩ Frequency Synthesizers with 800 MHz Integer PLL |

| LMX2485ESQX | 50 MHz - 3.0 GHz High Performance Delta-Sigma Low Power Dual PLLatinum⑩ Frequency Synthesizers with 800 MHz Integer PLL |

| LMX2485SQ | 50 MHz - 3.0 GHz High Performance Delta-Sigma Low Power Dual PLLatinum⑩ Frequency Synthesizers with 800 MHz Integer PLL |

| LMX2485SQX | 50 MHz - 3.0 GHz High Performance Delta-Sigma Low Power Dual PLLatinum⑩ Frequency Synthesizers with 800 MHz Integer PLL |

| LMX2487 | 3.0 GHz - 6.0 GHz High Performance Delta-Sigma Low Power Dual PLLatinum⑩ Frequency Synthesizers with 3.0 GHz Integer PLL |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LMX2485E EVAL | 功能描述:BOARD EVALUATION LMX2485E RoHS:否 類(lèi)別:編程器,開(kāi)發(fā)系統(tǒng) >> 評(píng)估演示板和套件 系列:PLLatinum™ 標(biāo)準(zhǔn)包裝:1 系列:PCI Express® (PCIe) 主要目的:接口,收發(fā)器,PCI Express 嵌入式:- 已用 IC / 零件:DS80PCI800 主要屬性:- 次要屬性:- 已供物品:板 |

| LMX2485E EVAL/NOPB | 功能描述:鎖相環(huán) - PLL RoHS:否 制造商:Silicon Labs 類(lèi)型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| LMX2485EEVAL | 功能描述:時(shí)鐘和定時(shí)器開(kāi)發(fā)工具 LMX2485E EVAL BOARD RoHS:否 制造商:Texas Instruments 產(chǎn)品:Evaluation Modules 類(lèi)型:Clock Conditioners 工具用于評(píng)估:LMK04100B 頻率:122.8 MHz 工作電源電壓:3.3 V |

| LMX2485EEVAL/NOPB | 功能描述:時(shí)鐘和定時(shí)器開(kāi)發(fā)工具 LMX2485E EVAL BOARD RoHS:否 制造商:Texas Instruments 產(chǎn)品:Evaluation Modules 類(lèi)型:Clock Conditioners 工具用于評(píng)估:LMK04100B 頻率:122.8 MHz 工作電源電壓:3.3 V |

| LMX2485ESQ | 制造商:NSC 制造商全稱(chēng):National Semiconductor 功能描述:50 MHz - 3.0 GHz High Performance Delta-Sigma Low Power Dual PLLatinum? Frequency Synthesizers with 800 MHz Integer PLL |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。