- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄30730 > LC7219M PLL FREQUENCY SYNTHESIZER, 160 MHz, PDSO24 PDF資料下載

參數(shù)資料

| 型號: | LC7219M |

| 元件分類: | PLL合成/DDS/VCOs |

| 英文描述: | PLL FREQUENCY SYNTHESIZER, 160 MHz, PDSO24 |

| 封裝: | MFP-24 |

| 文件頁數(shù): | 10/12頁 |

| 文件大小: | 212K |

| 代理商: | LC7219M |

LC7219, 7219M

No.3661–7/12

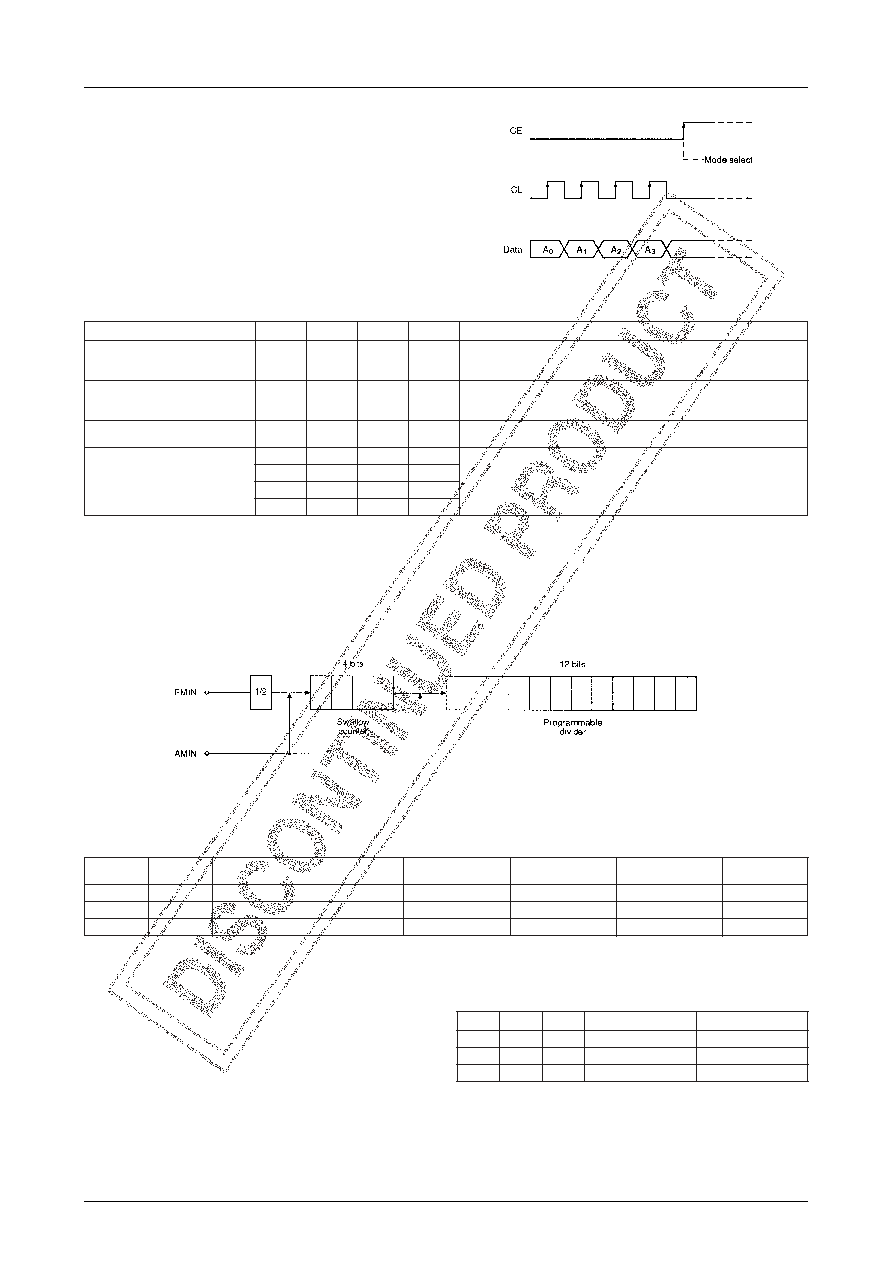

Serial Bus Data Transfer

The LC7219 and LC7219M can both transfer data in

three different modes-36-bit input data transfer, 24-bit

input data transfer and 28-bit output data transfer. The

transfer mode is selected by the four data bits on DI

immediately prior to CE going HIGH as shown in figure

6 and table 4. These bits are synchronized to the clock

and are latched into the mode register on the rising edge

of CE.

Note

× = don’t care

Programmable Divider

The configurration of the programmable divider is shown in figure 7. Input mode selection is shown in table 5.

Figure 6. Transfer mode select

Table 4. Mode selection

e

d

o

MA3

A2

A1

A0

n

o

i

t

p

i

r

c

s

e

D

t

u

p

n

i

a

t

a

d

l

a

i

r

e

s

t

i

b

-

6

3

0001

d

e

s

u

e

b

d

l

u

o

s

e

d

o

m

s

i

h

T

.

l

D

n

o

n

i

d

e

k

c

o

l

c

e

r

a

t

a

d

l

o

r

t

n

o

c

e

h

t

f

o

s

t

i

b

ll

A

e

h

t

y

f

i

d

o

m

o

t

d

e

s

u

e

b

o

s

l

a

n

a

c

t

I

.

e

c

i

v

e

d

e

h

t

e

z

il

a

i

t

i

n

i

o

t

p

u

-

r

e

w

o

p

r

e

t

f

a

R

s

t

i

b

f

o

s

e

u

l

a

v

0

R

o

t

1.

t

u

p

n

i

a

t

a

d

l

a

i

r

e

s

t

i

b

-

4

2

0010

o

t

d

e

s

u

s

i

e

d

o

m

s

i

h

T

.

l

D

n

o

n

i

d

e

k

c

o

l

c

e

r

a

t

a

d

l

o

r

t

n

o

c

e

h

t

f

o

s

t

i

b

4

2

e

h

t

d

n

a

s

t

i

b

t

r

o

p

t

u

p

t

u

o

e

h

t

,

s

t

i

b

o

i

t

a

r

e

i

v

i

d

e

l

b

a

m

a

r

g

o

r

p

e

h

t

u

p

n

i

.

t

i

b

e

l

b

a

n

e

r

e

t

n

u

o

c

e

s

o

p

r

u

p

-

l

a

r

e

n

e

g

t

u

p

t

u

o

a

t

a

d

l

a

i

r

e

s

0011

-

l

a

r

e

n

e

g

e

h

t

,

a

t

a

d

t

u

p

n

i

e

h

t

s

e

s

i

r

p

m

o

c

a

t

a

d

e

h

T

.

O

D

n

o

t

u

p

t

u

o

s

i

a

t

a

D

.

s

g

a

l

f

k

c

o

l

n

u

L

P

e

h

t

d

n

a

e

u

l

a

v

r

e

t

n

u

o

c

e

s

o

p

r

u

p

l

a

g

e

ll

I

0000

.

d

e

r

e

f

s

n

a

r

t

e

b

t

o

n

a

c

a

t

a

D

01

××

10

××

11

××

Figure 7. Programmable divider

Table 5. Programmable divider selection

V

DP

S)

z

H

M

(

e

g

n

a

r

y

c

n

e

u

q

e

r

f

t

u

p

n

Ir

e

d

i

v

i

d

2

/

1

7

1

/

1

d

n

a

6

1

/

1

r

e

w

o

ll

a

w

s

e

s

l

u

p

e

l

b

a

m

a

r

g

o

r

p

t

i

b

-

2

1

r

e

d

i

v

i

d

t

r

o

p

t

u

p

n

I

1

×

0

6

1

o

t

0

1

N

I

M

F

01

0

4

o

t

2–

N

I

M

A

00

0

.

0

1

o

t

5

.

0–

–

N

I

M

A

Note

× = don’t care

When an FM signal is input on FMIN, the actual divider

ratio is double the set ratio. For channel steps of 1, 5 and

9 kHz, a 3.6MHz crystal should be used. The program-

mable divider ratio is determined by the setting of the DV

and SP bits as shown in table 6.

Table 6. Divider ratio settings

V

DP

Sb

s

lo

i

t

a

r

t

e

So

i

t

a

r

l

a

u

t

c

A

1

×

0

D5

3

5

6

o

t

6

5

2o

i

t

a

r

t

e

s

e

c

i

w

T

01

0

D5

3

5

6

o

t

6

5

2o

i

t

a

r

t

e

S

00

4

D6

9

0

4

o

t

4o

i

t

a

r

t

e

S

Note

× = don’t care

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LC7230-8221 | SPECIALTY CONSUMER CIRCUIT, PQFP80 |

| LC7230-8272 | SPECIALTY CONSUMER CIRCUIT, PQFP80 |

| LC72323-XXXX | SPECIALTY CONSUMER CIRCUIT, PQFP80 |

| LC723341E | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| LC723341E | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LC7220 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| LC7221 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| LC7222 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| LC7223 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| LC7225 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。