- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374332 > KFG5616D1M-DEB (SAMSUNG SEMICONDUCTOR CO. LTD.) OneNAND256 PDF資料下載

參數(shù)資料

| 型號: | KFG5616D1M-DEB |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | OneNAND256 |

| 中文描述: | OneNAND256 |

| 文件頁數(shù): | 35/93頁 |

| 文件大小: | 1223K |

| 代理商: | KFG5616D1M-DEB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁當(dāng)前第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁

OneNAND256

FLASH MEMORY

35

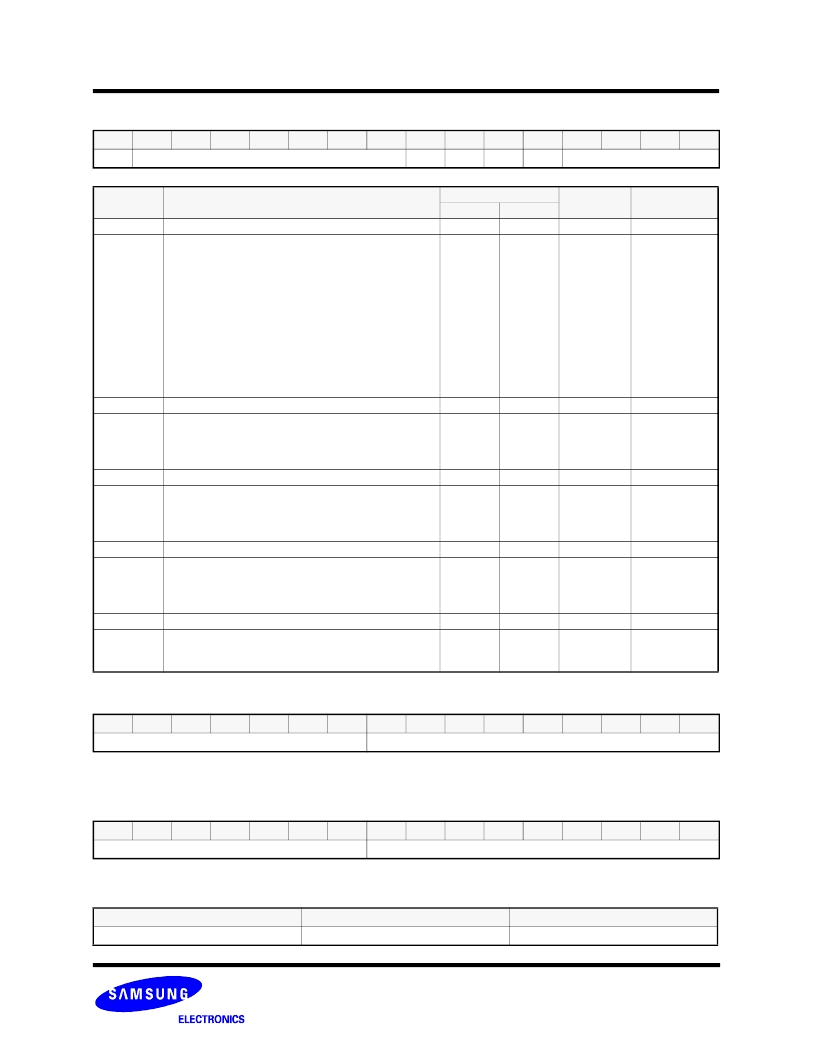

7.23 Interrupt Status Register (R/W): F241h,

default=8080h(after Cold reset),8010h(after Warm/Hot reset)

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

INT

Reserved(0000000)

RI

WI

EI

RSTI

Reserved(0000)

7.24 Start Block Address (R/W): F24Ch, default=0000h

SBA

(Start Block Address): Start NAND Flash block address in Write Protection mode, which preceeds ’Lock block command’ or ’Unlock block com-

mand’ or ’Lock-tight command’.

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Reserved(0000000)

SBA

7.25 End Block Address (R/W): F24Dh, default=0000h

EBA

(End Block Address): End NAND Flash block address in Write Protection mode, which preceeds ’Lock block command’ or ’Unlock block command’

or ’Lock-tight command’. EBA should be equal to or larger than SBA.

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Reserved(0000000)

EBA

Device

Number of Block

SBA/EBA

256Mb

512

[8:0]

Bit

Address

Bit Name

Default State

Cold

1

Valid

States

Function

Warm/Hot

1

15

INT(interrupt): the master interrupt bit

- Set to ’1’ of itself when one or more of RI, WI, EI and

RSTI is set to ’1’, or Unlock(0023h), Lock(002Ah), Lock-

tight(002Ch), Erase Verify Read(0071h), or OTP

access(0065h) operation, or "Load Data into Buffer" is

completed.

- Cleared to ’0’ when by writing ’0’ to this bit or by

reset(Cold/Warm/Hot reset).

’0’ in this bit means that INT pin is low status.

(This INT bit is directly wired to the INT pin on the chip.

INT pin goes low upon writing ’0’ to this bit when

INTpol is high and goes high upon writing ’0’ to this

bit when INTpol is low. )

RI(Read Interrupt):

- Set to ’1’ of itself at the completion of Load Operation

(0000h, 0013h, or boot is done.)

- Cleared to ’0’ when by writing ’0’ to this bit or by reset

(Cold/Warm/Hot reset).

WI(Write Interrupt):

- Set to ’1’ of itself at the completion of Program Operation

(0080h, 001Ah, or 001Bh)

- Cleared to ’0’ when by writing ’0’ to this bit or by reset

(Cold/Warm/Hot reset).

EI(Erase Interrupt):

- Set to ’1’ of itself at the completion of Erase Operation

(0094h, 0095h, or 0030h)

- Cleared to ’0’ when by writing ’0’ to this bit or by reset

(Cold/Warm/Hot reset).

RSTI(Reset Interrupt):

- Set to ’1’ of itself at the completion of Reset Operation

(00B0h, 00F0h, 00F3h, or warm reset is released.)

- Cleared to ’0’ when by writing ’0’ to this bit.

0

Interrupt Off

Interrupt Pending

0->1

7

1

0

0

Interrupt Off

Interrupt Pending

0->1

6

0

0

0

Interrupt Off

Interrupt Pending

0->1

5

0

0

0

Interrupt Off

Interrupt Pending

0->1

4

0

1

0

Interrupt Off

Interrupt Pending

0->1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| KFG5616Q1 | OneNAND256 |

| KFG5616Q1M | OneNAND256 |

| KFG5616Q1M-DEB | OneNAND256 |

| KFG5616U1M-DIB | OneNAND256 |

| KFM110 | SPECIFICATIONS FOR SAW FILTER(BAND PASS FILTERS FOR THR IF CIRCUITS OF CORDLESS PHONE) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| KFG5616Q1 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:OneNAND256 |

| KFG5616Q1A-DEB | 制造商:Samsung Semiconductor 功能描述: |

| KFG5616Q1A-DEB5 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:OneNAND Specification FLASH MEMORY |

| KFG5616Q1A-DEB6 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:OneNAND Specification FLASH MEMORY |

| KFG5616Q1A-PEB5 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:OneNAND Specification FLASH MEMORY |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。