- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374270 > K4H511638E-TCB0 (SAMSUNG SEMICONDUCTOR CO. LTD.) 128Mb DDR SDRAM PDF資料下載

參數(shù)資料

| 型號(hào): | K4H511638E-TCB0 |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 128Mb DDR SDRAM |

| 中文描述: | 128MB DDR SDRAM的 |

| 文件頁(yè)數(shù): | 10/24頁(yè) |

| 文件大小: | 367K |

| 代理商: | K4H511638E-TCB0 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)當(dāng)前第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)

Rev. 1.1 June. 2005

DDR SDRAM

DDR SDRAM 512Mb C-die (x4, x8, x16)

32M x 4Bit x 4 Banks / 16M x 8Bit x 4 Banks / 8M x 16Bit x 4 Banks Double Data Rate SDRAM

The K4H510438C / K4H510838C / K4H511638C is 536,870,912 bits of double data rate synchronous DRAM organized as 4x

33,554,432 / 4x 16,777,216 / 4x 8,388,608 words by 4/8/16bits, fabricated with SAMSUNG

′

s high performance CMOS technology. Syn-

chronous features with Data Strobe allow extremely high performance up to 400Mb/s per pin. I/O transactions are possible on both

edges of DQS. Range of operating frequencies, programmable burst length and programmable latencies allow the device to be useful

for a variety of high performance memory system applications.

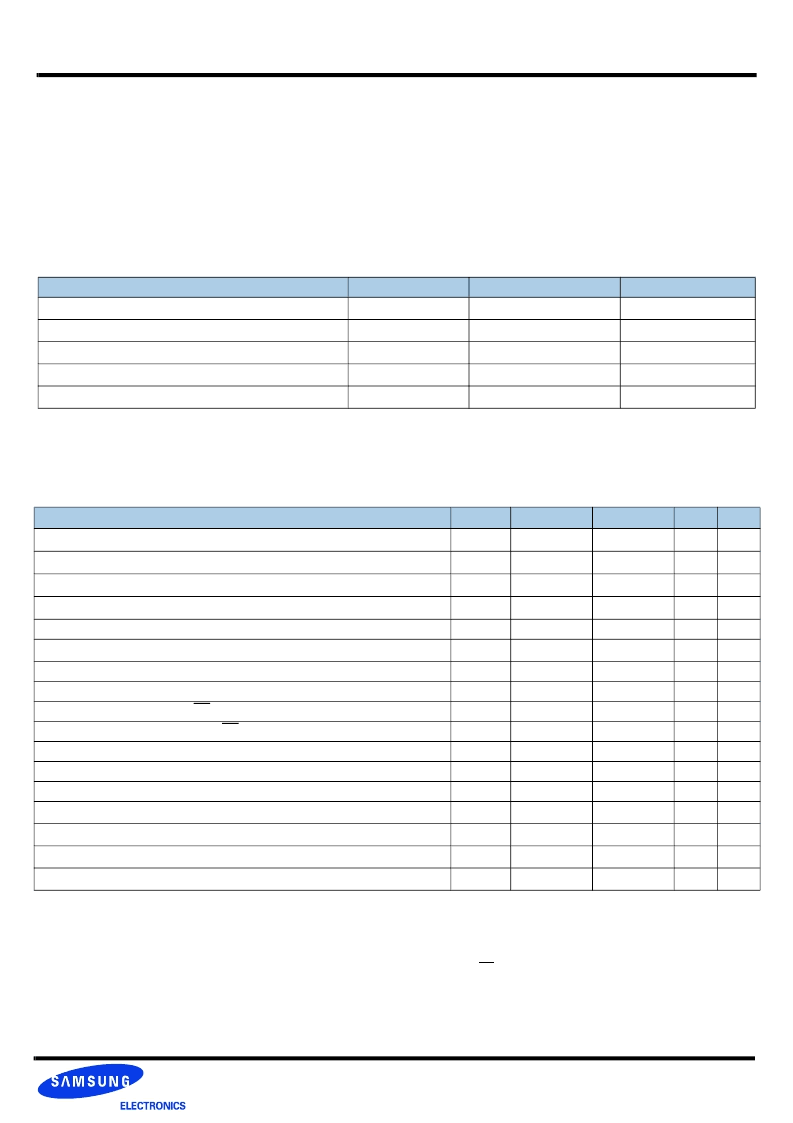

Note : Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded.

Functional operation should be restricted to recommend operation condition.

Exposure to higher than recommended voltage for extended periods of time could affect device reliability.

Parameter

Symbol

Value

Unit

Voltage on any pin relative to V

SS

V

IN

, V

OUT

-0.5 ~ 3.6

V

Voltage on V

DD

& V

DDQ

supply relative to V

SS

V

DD

, V

DDQ

-1.0 ~ 3.6

V

Storage temperature

T

STG

-55 ~ +150

°

C

Power dissipation

P

D

1.5

W

Short circuit current

I

OS

50

mA

Recommended operating conditions(Voltage referenced to V

SS

=0V, T

A

=0 to 70

°

C)

11.0 DC Operating Conditions

Note :

1. VREF is expected to be equal to 0.5*VDDQ of the transmitting device, and to track variations in the dc level of same. Peak-to peak noise on VREF may

not exceed +/-2% of the dc value.

2. V

TT

is not applied directly to the device. V

TT

is a system supply for signal termination resistors, is expected to be set equal to VREF, and must track vari-

ations in the DC level of VREF

3. VID is the magnitude of the difference between the input level on CK and the input level on CK.

4. The ratio of the pullup current to the pulldown current is specified for the same temperature and voltage, over the entire temperature and voltage range,

for device drain to source voltages from 0.25V to 1.0V. For a given output, it represents the maximum difference between pullup and pulldown drivers

due to process variation. The full variation in the ratio of the maximum to minimum pullup and pulldown current will not exceed 1.7 for device drain to

source voltages from 0.1 to 1.0.

Parameter

Symbol

Min

Max

Unit

Note

Supply voltage(for device with a nominal V

DD

of 2.5V for DDR266/333)

V

DD

2.3

2.7

Supply voltage(for device with a nominal V

DD

of 2.6V for DDR400)

V

DD

2.5

2.7

I/O Supply voltage(for device with a nominal V

DD

of 2.5V for DDR266/333)

V

DDQ

2.3

2.7

V

I/O Supply voltage(for device with a nominal V

DD

of 2.5V for DDR400)

V

DDQ

2.5

2.7

I/O Reference voltage

V

REF

0.49*VDDQ

0.51*VDDQ

V

1

I/O Termination voltage(system)

V

TT

V

REF

-0.04

V

REF

+0.04

V

2

Input logic high voltage

V

IH

(DC)

V

REF

+0.15

V

DDQ

+0.3

V

Input logic low voltage

V

IL

(DC)

-0.3

V

REF

-0.15

V

Input Voltage Level, CK and CK inputs

V

IN

(DC)

-0.3

V

DDQ

+0.3

V

Input Differential Voltage, CK and CK inputs

V

ID

(DC)

0.36

V

DDQ

+0.6

V

3

V-I Matching: Pullup to Pulldown Current Ratio

VI(Ratio)

0.71

1.4

-

4

Input leakage current

I

I

-2

2

uA

Output leakage current

I

OZ

-5

5

uA

Output High Current(Normal strengh driver) ;V

OUT

= V

TT

+ 0.84V

I

OH

-16.8

mA

Output High Current(Normal strengh driver) ;V

OUT

= V

TT

- 0.84V

I

OL

16.8

mA

Output High Current(Half strengh driver) ;V

OUT

= V

TT

+ 0.45V

I

OH

-9

mA

Output High Current(Half strengh driver) ;V

OUT

= V

TT

- 0.45V

I

OL

9

mA

9.0 General Description

10.0 Absolute Maximum Rating

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| K4H511638E-TLA0 | 128Mb DDR SDRAM |

| K4H511638E-TLA2 | 128Mb DDR SDRAM |

| K4H511638E-TLB0 | 128Mb DDR SDRAM |

| K4H510438C-UCA2 | 512Mb C-die DDR SDRAM Specification |

| K4H510438C-UCB0 | 512Mb C-die DDR SDRAM Specification |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| K4H511638E-TLA0 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:128Mb DDR SDRAM |

| K4H511638E-TLA2 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:128Mb DDR SDRAM |

| K4H511638E-TLB0 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:128Mb DDR SDRAM |

| K4H511638F | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:512Mb F-die DDR SDRAM Specification |

| K4H511638F-LC/LB3 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:512Mb F-die DDR SDRAM Specification |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。