- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383120 > IS82C89 (INTERSIL CORP) CMOS Bus Arbiter PDF資料下載

參數(shù)資料

| 型號: | IS82C89 |

| 廠商: | INTERSIL CORP |

| 元件分類: | 外設(shè)及接口 |

| 英文描述: | CMOS Bus Arbiter |

| 中文描述: | 8 MHz, BUS ARBITER AND CONT SIG GEN, PQCC20 |

| 封裝: | PLASTIC, LCC-20 |

| 文件頁數(shù): | 2/15頁 |

| 文件大?。?/td> | 123K |

| 代理商: | IS82C89 |

4-344

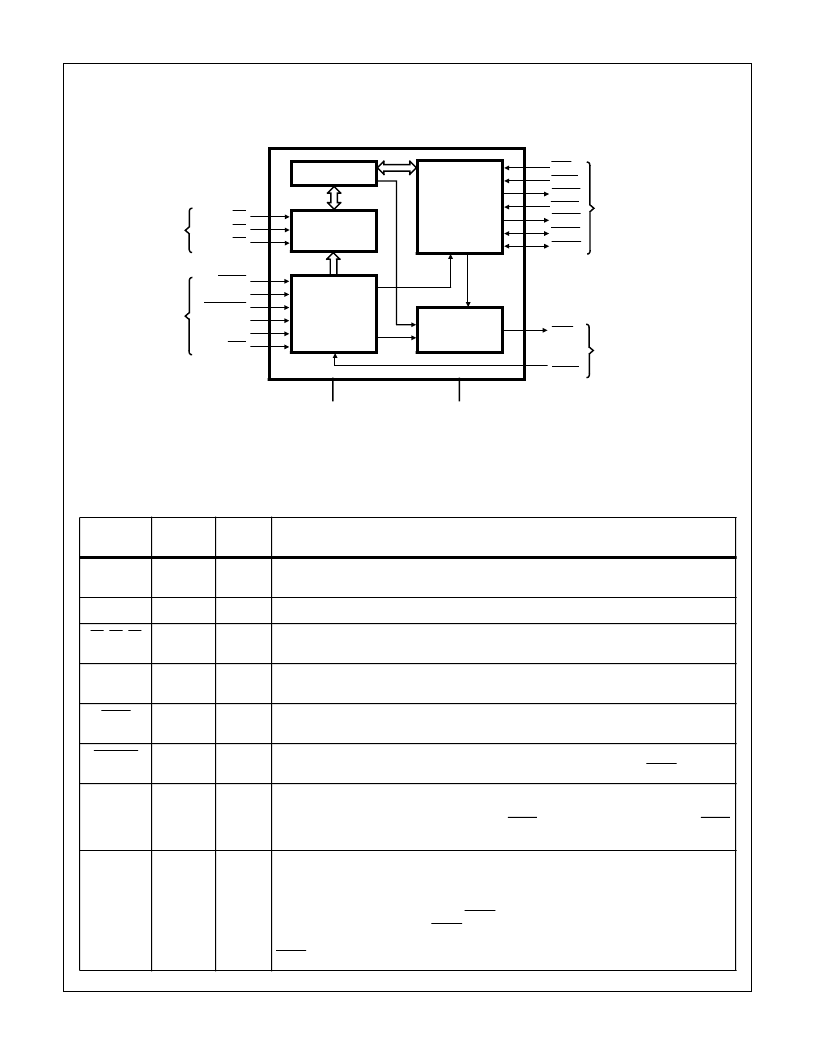

Functional Diagram

Pin Description

PIN

SYMBOL

NUMBER

TYPE

DESCRIPTION

V

CC

20

V

CC

: The +5V Power supply pin. A 0.1

μ

F capacitor between pins 10 and 20 is recommended for

decoupling.

GND

10

GROUND.

S0, S1, S2

1, 18-19

I

STATUS INPUT PINS: The status input pins from an 80C86, 80C88 or 8089 processor. The

82C89 decodes these pins to initiate bus request and surrender actions. (See Table 1).

CLK

17

I

CLOCK: From the 82C84A or 82C85 clock chip and serves to establish when bus arbiter actions

are initiated.

LOCK

16

I

LOCK: A processor generated signal which when activated (low) prevents the arbiter from surren-

dering the multi-master system bus to any other bus arbiter, regardless of its priority.

CRQLCK

15

I

COMMON REQUEST LOCK: An active low signal which prevents the arbiter from surrendering the

multi-master system bus to any other bus arbiter requesting the bus through the CBRQ input pin.

RESB

4

I

RESIDENT BUS: A strapping option to configure the arbiter to operate in systems having both a

multi-master system bus and a Resident Bus. Strapped high, the multi-master system bus is re-

quested or surrendered as a function of the SYSB/RESB input pin. Strapped low, the SYSB/RESB

input is ignored.

ANYRQST

14

I

ANY REQUEST: A strapping option which permits the multi-master system bus to be surrendered

to a lower priority arbiter as if it were an arbiter of higher priority (i.e., when a lower priority arbiter

requests the use of the multi-master system bus, the bus is surrendered as soon as it is possible).

When ANYRQST is strapped low, the bus is surrendered according to Table A in Design Informa-

tion. If ANYRQST is strapped high and CBRQ is activated, the bus is surrendered at the end of

the present bus cycle. Strapping CBRQ low and ANYRQST high forces the 82C89 arbiter to sur-

render the multi-master system bus after each transfer cycle. Note that when surrender occurs

BREQ is driven false (high).

CONTROL

ARBITRATION

MULTIBUS

INTERFACE

LOCAL

BUS

INTERFACE

+5V

GND

CONTROL/

STRAPPING

OPTIONS

80C86/

80C88

STATUS

COMMAND

SIGNALS

MULTIBUS

TM

SYSTEM

SIGNALS

MULTIBUS

TM

IS AN INTEL CORP. TRADEMARK

BPRN

BPRO

BUSY

CBRQ

SYSB/

RESB

INIT

BCLK

BREQ

AEN

CLK

RESB

ANYRQST

LOCK

S1

S0

IOB

CRQLCK

S2

STATUS

DECODER

82C89

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IS9-1715ARH-8 | Radiation Hardened Complementary Switch FET Driver |

| IS-1715ARH | Radiation Hardened Complementary Switch FET Driver |

| IS9-1715ARH-Q | Radiation Hardened Complementary Switch FET Driver |

| ISD-200 | USB Mass Storage Class Bulk-Only Specification Compliant |

| ISD-T267SP | DIGITAL SPEECH PROCESSOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IS82D | 制造商:IDEC CORPORATION 功能描述:SENS.IND. 2W/F 24-230VAC NC |

| IS82DK | 制造商:IDEC CORPORATION 功能描述:SENS.IND. 2W/F 24-230VAC NC |

| IS82DL | 制造商:IDEC CORPORATION 功能描述:SENS.IND. 2W/F 24-230VAC NC |

| IS82K | 制造商:IDEC CORPORATION 功能描述:SENS.IND. 2W/F 24-230VAC NC |

| IS82L | 制造商:IDEC CORPORATION 功能描述:SENS.IND. 2W/F 24-230VAC NC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。