- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383120 > IS82C59A-5 (HARRIS SEMICONDUCTOR) CMOS Priority Interrupt Controller PDF資料下載

參數(shù)資料

| 型號(hào): | IS82C59A-5 |

| 廠商: | HARRIS SEMICONDUCTOR |

| 元件分類: | 中斷控制器 |

| 英文描述: | CMOS Priority Interrupt Controller |

| 中文描述: | 80C86; 80C88; 80C286; 8080; 8085; 8086; 8088; 80286; NSC800 COMPATIBLE, INTERRUPT CONTROLLER, PQCC28 |

| 文件頁(yè)數(shù): | 14/20頁(yè) |

| 文件大小: | 152K |

| 代理商: | IS82C59A-5 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)當(dāng)前第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)

4-14

This modification forces the use of software programming to

determine whether the 82C59A is a master or a slave. Bit 3

in ICW4 programs the buffered mode, and bit 2 in lCW4

determines whether it is a master or a slave.

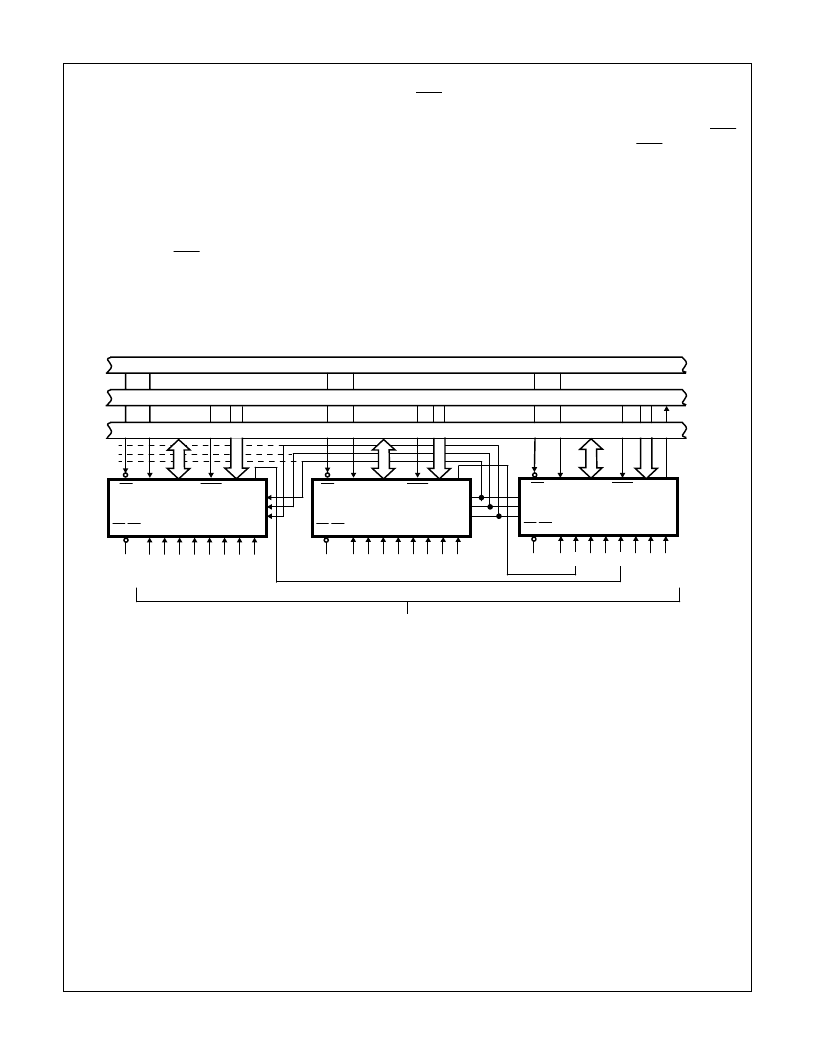

Cascade Mode

The 82C59A can be easily interconnected in a system of

one master with up to eight slaves to handle up to 64 priority

levels.

The master controls the slaves through the 3 line cascade

bus (CAS2 - 0). The cascade bus acts like chip selects to the

slaves during the INTA sequence.

In a cascade configuration, the slave interrupt outputs (INT)

are connected to the master interrupt request inputs. When

a slave request line is activated and afterwards acknowl-

edged, the master will enable the corresponding slave to

release the device routine address during bytes 2 and 3 of

INTA. (Byte 2 only for 80C86/88/286).

The cascade bus lines are normally low and will contain the

slave address code from the leading edge of the first INTA

pulse to the trailing edge of the last INTA pulse. Each

82C59A in the system must follow a separate initialization

sequence and can be programmed to work in a different

mode. An EOI command must be issued twice: once for the

master and once for the corresponding slave. Chip select

decoding is required to activate each 82C59A.

NOTE: Auto EOI is supported in the slave mode for the 82C59A.

The cascade lines of the Master 82C59A are activated only

for slave inputs, non-slave inputs leave the cascade line

inactive (low). Therefore, it is necessary to use a slave

address of 0 (zero) only after all other addresses are used.

FIGURE 11. CASCADING THE 82C59A

CS

82C59A

SLAVE A

CINT

CAS 1

CAS 2

1

A

0

D

7

- D

0

INTA

SP/EN 7

5

6

4

3

2

0

GND

7

5

6

4

3

2

1

0

CS

82C59A

SLAVE B

CINT

CAS 1

CAS 2

1

A

0

D

7

- D

0

INTA

SP/EN 7

5

6

4

3

2

0

GND

7

5

6

4

3

2

1

0

CS

MASTER 82C59A

CAS 0

CAS 1

CAS 2

SP/EN 7

INT

A

0

D

7

- D

0

INTA

5

6

4

3

2

1

0

V

CC

7

5

4

2

1

0

3

6

INT REQ

DATA BUS (8)

CONTROL BUS

ADDRESS BUS (16)

INTERRUPT REQUESTS

82C59A

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IS82C86H | CMOS Octal Bus Transceiver |

| IS82C86H-5 | CMOS Octal Bus Transceiver |

| IS82C87H | CMOS Octal Inverting Bus Transceiver |

| IS82C87H-5 | CMOS Octal Inverting Bus Transceiver |

| IS82C88 | CMOS Bus Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IS82C59AX96 | 功能描述:IC CTRLR INTERRUPT 8MHZ 28-PLCC RoHS:否 類別:集成電路 (IC) >> 接口 - 控制器 系列:- 標(biāo)準(zhǔn)包裝:4,900 系列:- 控制器類型:USB 2.0 控制器 接口:串行 電源電壓:3 V ~ 3.6 V 電流 - 電源:135mA 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:36-VFQFN 裸露焊盤 供應(yīng)商設(shè)備封裝:36-QFN(6x6) 包裝:* 其它名稱:Q6396337A |

| IS82C59AZ | 功能描述:接口-I/O擴(kuò)展器 PERIPH INT CNTRLR 5V 8MHZ 28PLCC IND RoHS:否 制造商:NXP Semiconductors 邏輯系列: 輸入/輸出端數(shù)量: 最大工作頻率:100 kHz 工作電源電壓:1.65 V to 5.5 V 工作溫度范圍:- 40 C to + 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:HVQFN-16 封裝:Reel |

| IS82C59AZX96 | 功能描述:接口-I/O擴(kuò)展器 PERIPH INT CNTRLR 5V 8MHZ 28PLCC IND RoHS:否 制造商:NXP Semiconductors 邏輯系列: 輸入/輸出端數(shù)量: 最大工作頻率:100 kHz 工作電源電壓:1.65 V to 5.5 V 工作溫度范圍:- 40 C to + 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:HVQFN-16 封裝:Reel |

| IS82C600 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:TRAILBLAZER High-Speed SRAM with Address Decoding and Ready Logic |

| IS82C82 | 制造商:Rochester Electronics LLC 功能描述: 制造商:Harris Corporation 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。