- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360907 > IPM6210CA-T Analog IC PDF資料下載

參數(shù)資料

| 型號: | IPM6210CA-T |

| 英文描述: | Analog IC |

| 中文描述: | 模擬IC |

| 文件頁數(shù): | 13/15頁 |

| 文件大小: | 343K |

| 代理商: | IPM6210CA-T |

13

output ripple voltage and the initial voltage drop after a

transient. In most cases, multiple electrolytic capacitors of small

case size perform better than a single large case capacitor.

MOSFET Selection and Considerations

Requirements for the upper and lower MOSFETs are

different in mobile applications. The reason for that is the

10:1 difference in conduction time of the lower and the upper

MOSFETs driven by a difference between the input voltage

which is nominally in the range from 8V to 20V, while

nominal output voltage is about 1.5V.

Requirements for the lower MOSFET are simpler than

those to the upper one. The lower the r

DS(ON)

of this

device, the lower the conduction losses, the higher the

converter’s efficiency. Switching losses and gate drive

losses are not significant because of zero-voltage switching

conditions inherent for this device in the buck converter.

Low reverse recovery charge of the body diode is important

because it causes shoot-trough current spikes when the

upper MOSFET turns on. Also, important is to verify that

the lower MOSFET gate voltage does not reach threshold

when high dV/dt transition occurs on the phase node. To

minimize this effect, IPM6210 has a low, 0.8

typical, low

side driver pull-down resistance.

Requirements to the upper MOSFET r

DS(ON)

are less

stringent than to the lower MOSFET because its conduction

time is significantly shorter so switching losses can dominate

especially at higher input voltages. It is recommended to have

equal conduction and switching losses in the upper MOSFET

at the nominal input voltage and load current. Then the

maximum of the converter efficiency is tuned to the operating

point where it is most desired. Also, this provides the most

cost effective solution.

Precise calculation of power dissipation in the MOSFETs is

very complex because many parameters affecting turn-on

and turn-off times such as gate reverse transfer charge, gate

internal resistance, body diode reverse recovery charge,

package and layout impedances and their variation with the

operation conditions are not available to a designer. The

following equations are provided only for rough estimation of

the power losses and should be accompanied by a detailed

breadboard evaluation. Attention should be paid to the input

voltage extremes where power dissipation in the MOSFETs

is usually higher.

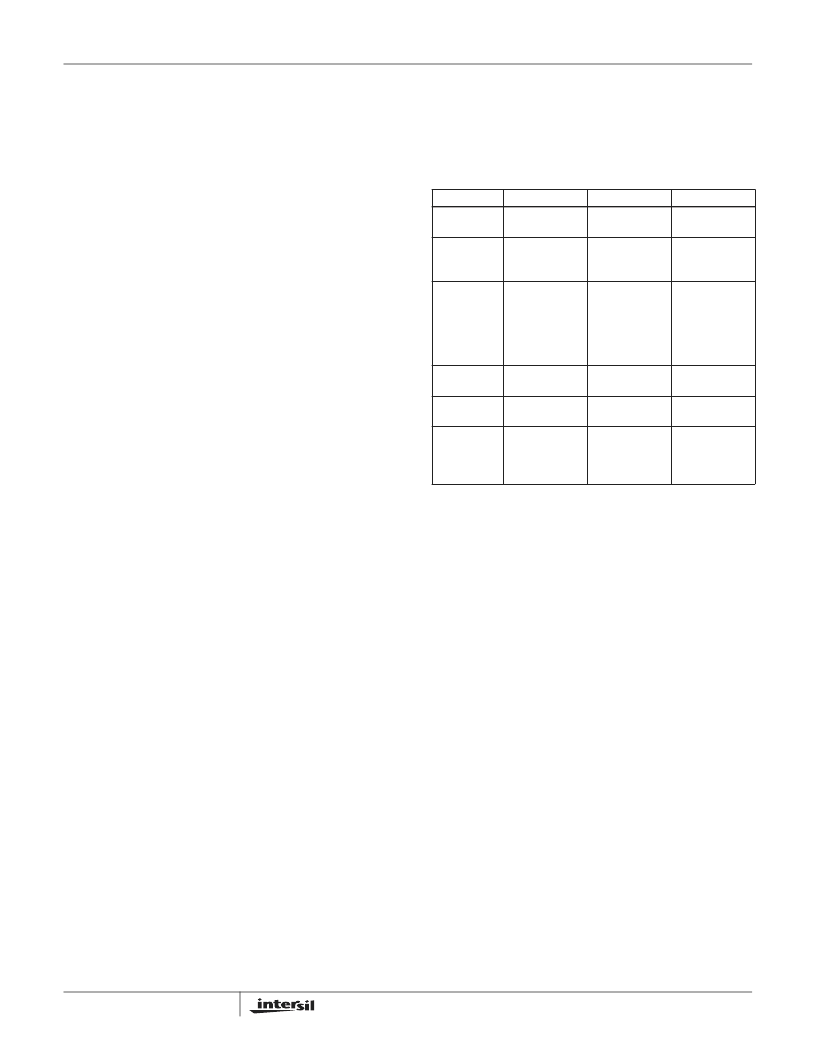

Table 2 provides some component information for several

typical applications.

Layout Considerations

Switching converters, even during normal operation,

produce short pulses of current which could cause

substantial ringing and be a source of EMI pollution if layout

constrains are not observed.

There are two sets of critical components in a DC-DC

converter. The switching power components process large

amounts of energy at high rate and though, usually appear

to be a source of a noise, end a low power components

responsible for bias and feedback functions, though appear

to be mainly recipients of the noise. The situation with the

IPM6210 control IC is even more critical as it provides

control functions for two independent converters and poor

layout design could lead to cross talk between the

converters and result in degradation in the performance.

A multi-layer printed circuit board is recommended.

Dedicate one solid layer for a ground plane. Dedicate

another solid layer as a power plane and break this plane

into smaller island of common voltage levels.

Notice all the nodes that are subjected to high dV/dt voltage

swing as PHASE1,2 nodes, for example. All surrounding

circuitry will tend to couple the noise from these nodes

trough stray capacitance. Do not oversize copper traces

connected to these nodes. Do not place traces connected to

the feedback components adjacent to these traces.

Keep the wiring traces from the control IC to the MOSFET

gate and source as short as possible and capable to handle

peak currents up to 2A. Minimize the area within the gate-

source path to reduce stray inductance and eliminate

parasitic ringing at the gate.

Locate small critical components like the soft-start capacitor

and current sense resistors as close, as possible to the

respective pins of the IC.

P

UPPER

Io

2

----------------------------------------------------------

r

IN

V

(

)

×

Io

---------------------------------------------------------------

V

xFs

ton

toff

+

×

×

+

=

P

LOWER

Io

2

r

DS ON

)

×

1

V

IN

---------------

–

×

=

TABLE 2

COMPONENT

Maximum

CPU Current

Inductor

CIRCUIT 1

8.0A

CIRCUIT 2

12.0A

CIRCUIT 3

18.0A

2.0

μ

H

Panasonic

ETQP6F2R0BFA

3x270

μ

F

Panasonic

EEFUE0D271R

or

Sanyo

4x2R5TPC220M

1.0

μ

H

Panasonic

ETQP6F2R0BFA

5x270

μ

F

Panasonic

EEFUE0D271R

or

Sanyo

6x2R5TPC220M

0.8

μ

H

Panasonic

ETQP6F2R0BFA

6x270

μ

F

Panasonic

EEFUE0D271R

Output

Capacitor

High-Side

MOSFET

Low-Side

MOSFET

Current-Input

Resistor

for

~6% Droop At

V

O

= 1.6V

HUF76112SK8

HUF76112SK8

2x

ITF86130SK8T

1.00k

2x

HUF76112SK8

2x

ITF86130SK8T

1.50k

ITF86130SK8T

1.27k

IPM6210

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IPM6220CB | Analog IC |

| IPM6210CA | Analog IC |

| IPS0551T(SMD220) | TRANSISTOR | MOSFET | N-CHANNEL | 37V V(BR)DSS | TO-273VAR |

| IPS0551T(TO220) | TRANSISTOR | MOSFET | N-CHANNEL | 37V V(BR)DSS | TO-273AA |

| IPS511E | PERIPHERAL DRIVER|1 DRIVER|MOS|LLCC|18PIN|CERAMIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IPM6220 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Advanced Triple PWM and Dual Linear Power Controller for Portable |

| IPM6220A | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Advanced Triple PWM and Dual Linear Power Controller for Portable Applications |

| IPM6220ACA | 制造商:Rochester Electronics LLC 功能描述:30V CS80,FSC PROCESS WITH IMPROVED ESD STRUCTURE - Bulk 制造商:Intersil Corporation 功能描述: |

| IPM6220ACAZ | 功能描述:電流型 PWM 控制器 30V CS80 FSC PROCESS W/IMPROVED ESD STRUC RoHS:否 制造商:Texas Instruments 開關(guān)頻率:27 KHz 上升時間: 下降時間: 工作電源電壓:6 V to 15 V 工作電源電流:1.5 mA 輸出端數(shù)量:1 最大工作溫度:+ 105 C 安裝風格:SMD/SMT 封裝 / 箱體:TSSOP-14 |

| IPM6220ACAZA-T | 功能描述:電流型 PWM 控制器 W/ANEAL 30V CS80 FSC PROCESS W/IMPROVED RoHS:否 制造商:Texas Instruments 開關(guān)頻率:27 KHz 上升時間: 下降時間: 工作電源電壓:6 V to 15 V 工作電源電流:1.5 mA 輸出端數(shù)量:1 最大工作溫度:+ 105 C 安裝風格:SMD/SMT 封裝 / 箱體:TSSOP-14 |

發(fā)布緊急采購,3分鐘左右您將得到回復。