- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄239726 > IP80C31-12D (TEMIC SEMICONDUCTORS) 8-BIT, 12 MHz, MICROCONTROLLER, PDIP40 PDF資料下載

參數(shù)資料

| 型號: | IP80C31-12D |

| 廠商: | TEMIC SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, 12 MHz, MICROCONTROLLER, PDIP40 |

| 文件頁數(shù): | 121/170頁 |

| 文件大小: | 4133K |

| 代理商: | IP80C31-12D |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁當(dāng)前第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁

54

ATtiny4/5/9/10 [DATASHEET]

8127F–AVR–02/2013

11.3

Clock Sources

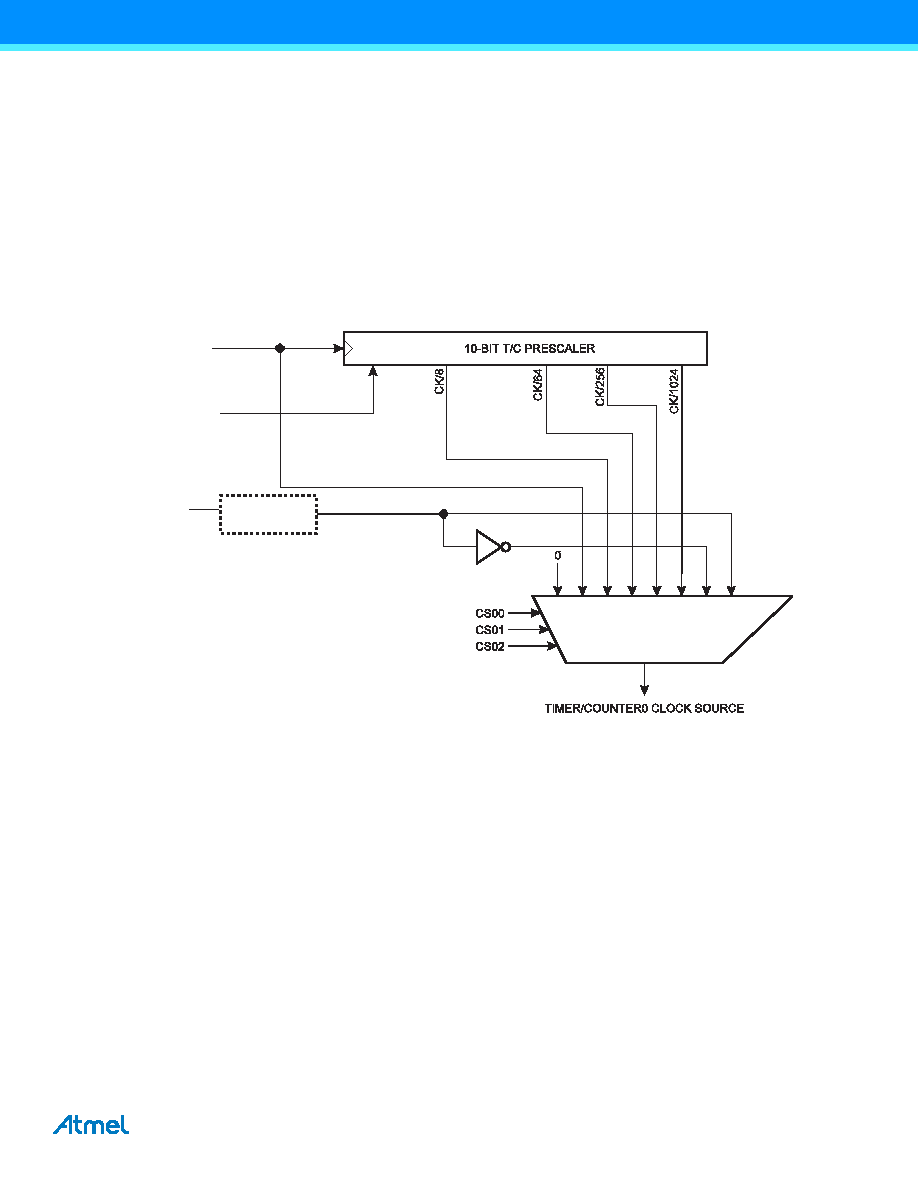

The Timer/Counter can be clocked by an internal or an external clock source. The clock source is selected by the

Clock Select logic which is controlled by the Clock Select (CS02:0) bits located in the Timer/Counter control Regis-

ter B (TCCR0B). For details on clock sources and prescaler, see section “Prescaler”.

11.3.1

Prescaler

The Timer/Counter can be clocked directly by the system clock (by setting the CS2:0 = 1). This provides the fastest

operation, with a maximum Timer/Counter clock frequency equal to system clock frequency (f

CLK_I/O). Alternatively,

one of four taps from the prescaler can be used as a clock source.

See Figure 11-2 for an illustration of the prescaler unit.

Figure 11-2.

Prescaler for Timer/Counter0

Note:

1. The synchronization logic on the input pins (

T0) is shown in Figure 11-3 on page 55.

The prescaled clock has a frequency of f

75 for details.

11.3.1.1

Prescaler Reset

The prescaler is free running, i.e., operates independently of the Clock Select logic of the Timer/CounterCounter,

and it is shared by the Timer/Counter Tn. Since the prescaler is not affected by the Timer/Counter’s clock select,

the state of the prescaler will have implications for situations where a prescaled clock is used. One example of

prescaling artifacts occurs when the timer is enabled and clocked by the prescaler (CS2:0 = 2, 3, 4, or 5). The num-

ber of system clock cycles from when the timer is enabled to the first count occurs can be from 1 to N+1 system

clock cycles, where N equals the prescaler divisor (8, 64, 256, or 1024).

It is possible to use the Prescaler Reset for synchronizing the Timer/Counter to program execution.

PSR10

Clear

clk

T0

T0

clk

I/O

Synchronization

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IP80C51T-L16D | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PDIP40 |

| IV80C51T-30D | 8-BIT, MROM, 30 MHz, MICROCONTROLLER, PQFP44 |

| IV80C51-30D | 8-BIT, MROM, 30 MHz, MICROCONTROLLER, PQFP44 |

| IF280C31-36D | 8-BIT, 36 MHz, MICROCONTROLLER, PQFP44 |

| IF180C51T-36D | 8-BIT, MROM, 36 MHz, MICROCONTROLLER, PQFP44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IP80C31-16 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| IP80C31-20 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| IP80C31-25 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| IP80C31-30 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| IP80C31-36 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。