19 of 59

May 25, 2004

IDT 79RC32438

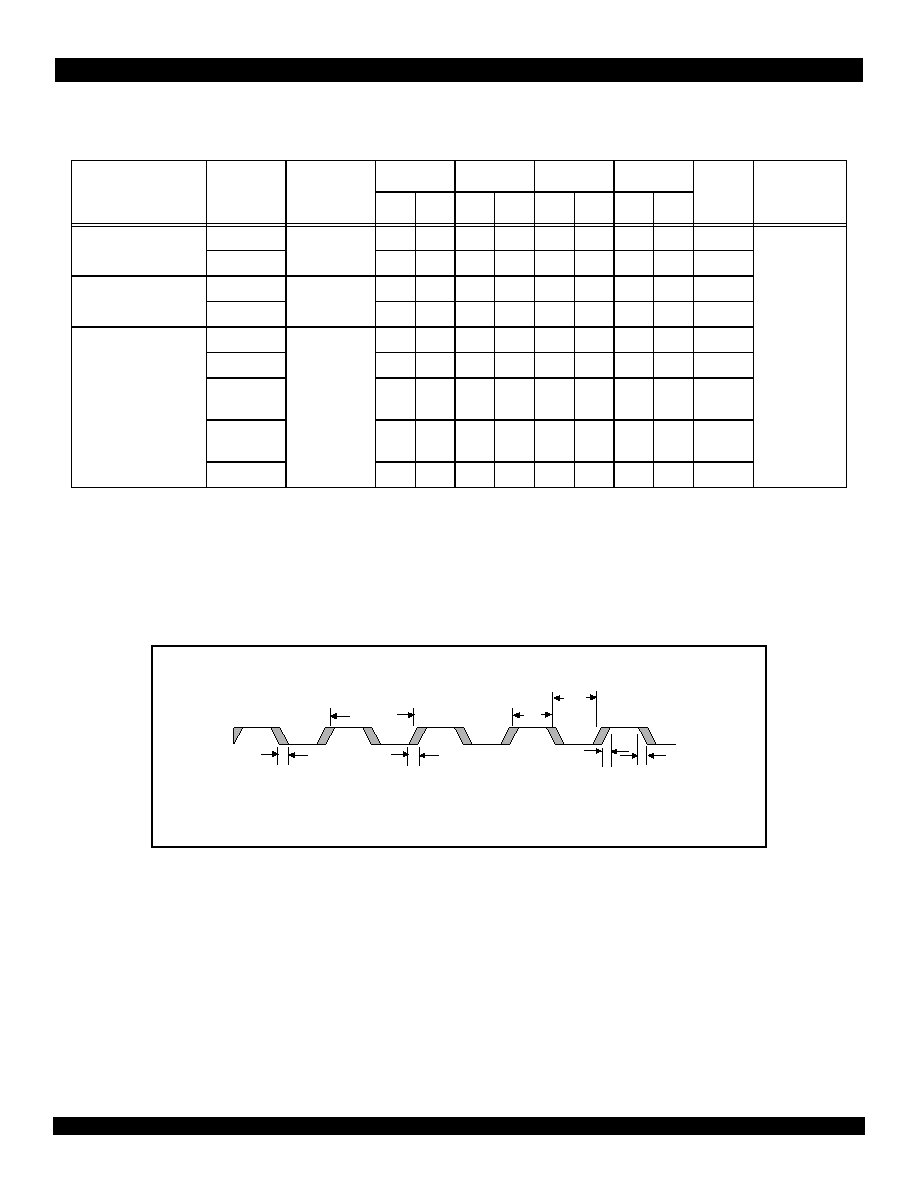

System Clock Parameters

Values based on systems running at recommended supply voltages and operating temperatures, as shown in Tables

15 and

16.Figure 3 Clock Parameters Waveform

Parameter

Symbol

Reference

Edge

200MHz

233MHz

266MHz

300MHz

Units

Timing

Diagram

Reference

Min

Max

Min

Max

Min

Max

Min

Max

PCLK1

1. The CPU pipeline clock (PCLK) speed is selected during cold reset by the boot configuration vector (see Table 3). Frequency

none

200

233

200

266

200

300

MHz

Tper

5.0

4.2

5.0

3.8

5.0

3.3

5.0

ns

ICLK2,3,4

2. ICLK is the internal IPBus clock. It is always equal to PCLK divided by 2. This clock cannot be sampled externally.

3. The ethernet clock (MIIxRXCLK and MIIxTXCLK) frequency must be equal to or less than 1/2 ICLK (MIIxRXCLK and MIIxTXCLK <= 1/2(ICLK)).

4. PCICLK must be equal to or less than two times ICLK (PCICLK <= 2(ICLK)) with a maximum PCICLK of 66MHz.

Frequency

none

100

116.5

100

133

100

150

MHz

Tper

10.0

8.5

10.0

7.5

6.7

10.0

ns

CLK5

5. The input clock (CLK) is input from the external oscillator to the internal PLL.

Frequency

none

25

66.6

25

77.6

25

88.6

25

100

MHz

Tper_5a

15.0

40.0

12.9

40.0

11.2

40.0

10

40

ns

Thigh_5a,

Tlow_5a

40

60

40

60

40

60

40

60

% of

Tper_5a

Trise_5a,

Tfall_5a

—3.0

ns

Tjitter_5a

—

0.1

—

0.1

—

0.1

—

0.1

ns

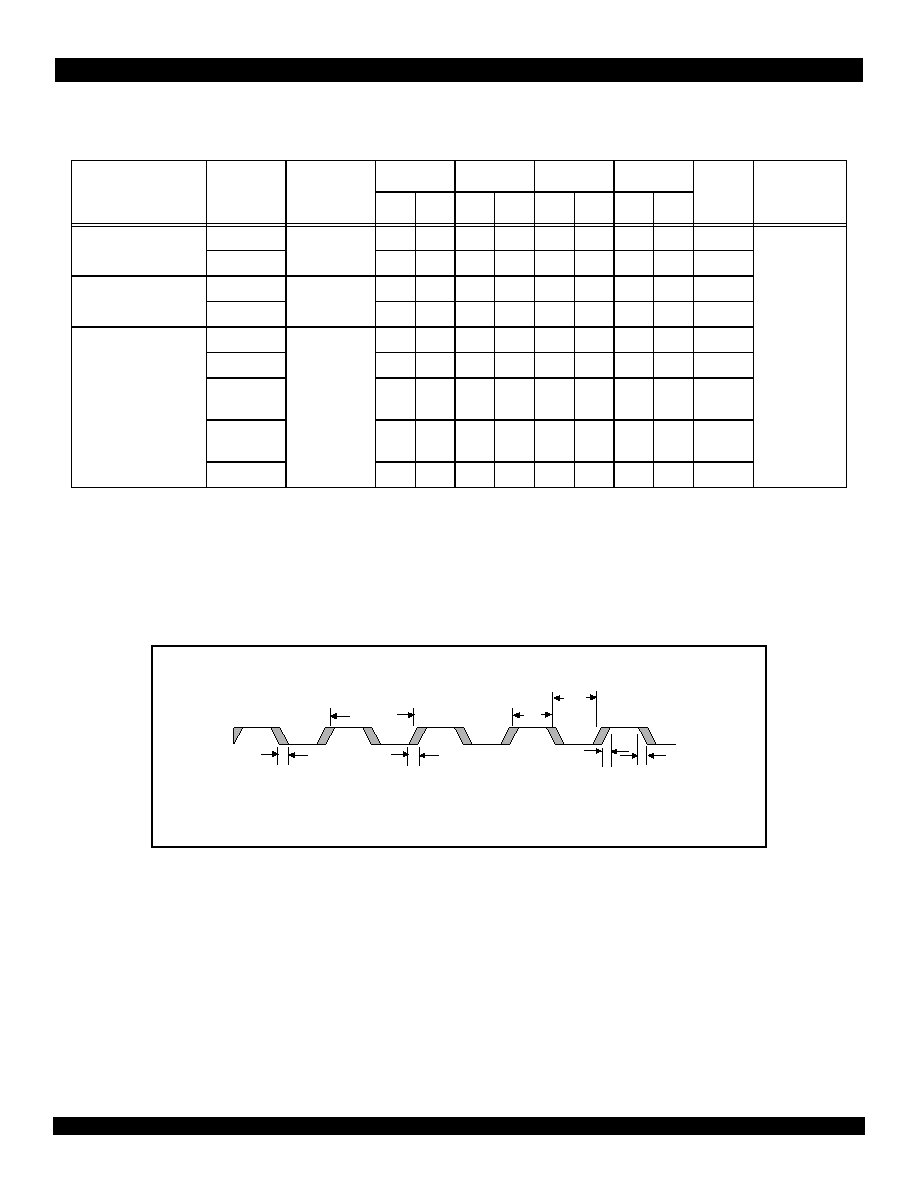

Table 5 Clock Parameters

Tlow_5a

Thigh_5a

Tper_5a

CLK

Trise_5a

Tfall_5a

Tjitter_5a