- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄9979 > IDT72V265LA15TFGI8 (IDT, Integrated Device Technology Inc)IC FIFO SS 16384X18 15NS 64STQFP PDF資料下載

參數(shù)資料

| 型號: | IDT72V265LA15TFGI8 |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁數(shù): | 27/27頁 |

| 文件大小: | 0K |

| 描述: | IC FIFO SS 16384X18 15NS 64STQFP |

| 標(biāo)準(zhǔn)包裝: | 1,250 |

| 系列: | 72V |

| 功能: | 同步 |

| 存儲(chǔ)容量: | 288K(16K x 18) |

| 數(shù)據(jù)速率: | 67MHz |

| 訪問時(shí)間: | 15ns |

| 電源電壓: | 3 V ~ 3.6 V |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 64-LQFP |

| 供應(yīng)商設(shè)備封裝: | 64-TQFP(10x10) |

| 包裝: | 帶卷 (TR) |

| 其它名稱: | 72V265LA15TFGI8 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁當(dāng)前第27頁

9

IDT72V255LA/72V265LA 3.3 VOLT CMOS SuperSync FIFO

8,192 x 18, 16,384 x 18

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

OCTOBER 22, 2008

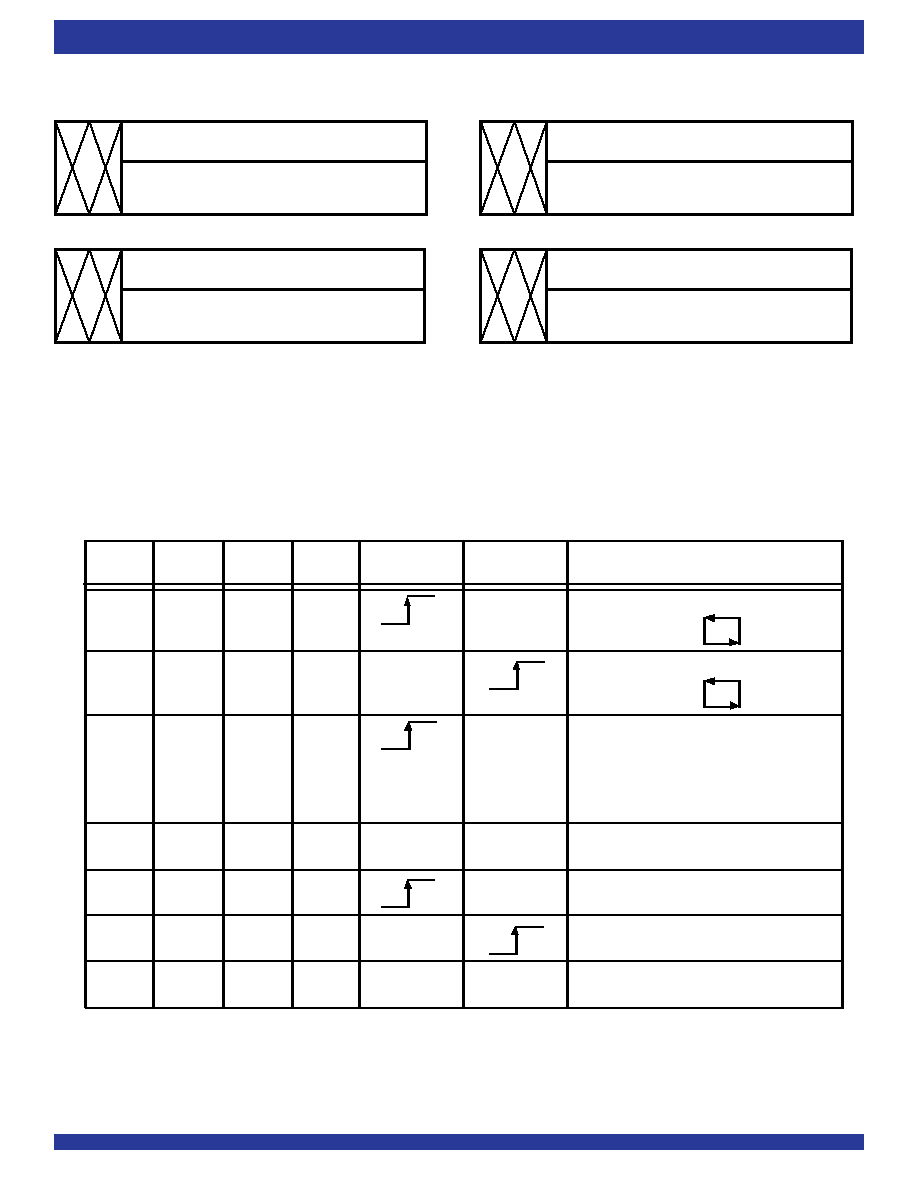

Figure 4. Programmable Flag Offset Programming Sequence

NOTES:

1. The programming method can only be selected at Master Reset.

2. Parallel reading of the offset registers is always permitted regardless of which programming method has been selected.

3. The programming sequence applies to both IDT Standard and FWFT modes.

Figure 3. Offset Register Location and Default Values

EMPTY OFFSET REGISTER

17

0

07FH if LD is LOW at Master Reset,

3FFH if LD is HIGH at Master Reset

FULL OFFSET REGISTER

17

0

DEFAULT VALUE

07FH if LD is LOW at Master Reset,

3FFH if LD is HIGH at Master Reset

12

IDT72V255LA

8,192 x 18 - BIT

4672 drw 06

EMPTY OFFSET REGISTER

17

0

07FH if LD is LOW at Master Reset,

3FFH if LD is HIGH at Master Reset

FULL OFFSET REGISTER

17

0

DEFAULT VALUE

07FH if LD is LOW at Master Reset,

3FFH if LD is HIGH at Master Reset

13

IDT72V265LA

16,384 x 18 - BIT

Selection

Parallel write to registers:

Empty Offset

Full Offset

Parallel read from registers:

Empty Offset

Full Offset

No Operation

Write Memory

Read Memory

No Operation

4672 drw 07

LD

0

X

1

0

WEN

0

1

0

X

1

REN

1

0

1

X

0

1

Serial shift into registers:

26 bits for the 72V255LA

28 bits for the 72V265LA

SEN

1

X

0

WCLK

X

RCLK

X

1 bit for each rising WCLK edge

Starting with Empty Offset (LSB)

Ending with Full Offset (MSB)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| KAD5512HP-17Q48 | IC ADC 12BIT 170MSPS SGL 48-QFN |

| HI5746KCAZ | CONV A/D 10BIT 40MSPS 28-SSOP |

| HI5746KCBZ | CONV A/D 10BIT 40MSPS 28-SOIC |

| MS27467T17B6PB | CONN PLUG 6POS STRAIGHT W/PINS |

| MS27472T12B98PA | CONN RCPT 10POS WALL MT W/PINS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT72V265LA15TFI | 功能描述:IC FIFO SS 16384X18 15NS 64STQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:74ABT 功能:同步,雙端口 存儲(chǔ)容量:4.6K(64 x 36 x2) 數(shù)據(jù)速率:67MHz 訪問時(shí)間:- 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:120-LQFP 裸露焊盤 供應(yīng)商設(shè)備封裝:120-HLQFP(14x14) 包裝:托盤 產(chǎn)品目錄頁面:1005 (CN2011-ZH PDF) 其它名稱:296-3984 |

| IDT72V265LA15TFI8 | 功能描述:IC FIFO SS 16384X18 15NS 64STQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72V265LA20PF | 功能描述:IC FIFO SS 16384X18 20NS 64-TQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72V265LA20PF8 | 功能描述:IC FIFO SS 16384X18 20NS 64-TQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72V265LA20TF | 功能描述:IC FIFO SS 16384X18 20NS 64STQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。