- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄10066 > IDT72V223L7-5PF8 (IDT, Integrated Device Technology Inc)IC FIFO 512X18 7-5NS 80QFP PDF資料下載

參數(shù)資料

| 型號: | IDT72V223L7-5PF8 |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁數(shù): | 25/45頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC FIFO 512X18 7-5NS 80QFP |

| 標(biāo)準(zhǔn)包裝: | 750 |

| 系列: | 72V |

| 功能: | 異步,同步 |

| 存儲容量: | 9.2K(512 x 18) |

| 數(shù)據(jù)速率: | 133MHz |

| 訪問時間: | 5ns |

| 電源電壓: | 3.15 V ~ 3.45 V |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 80-LQFP |

| 供應(yīng)商設(shè)備封裝: | 80-TQFP(14x14) |

| 包裝: | 帶卷 (TR) |

| 其它名稱: | 72V223L7-5PF8 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當(dāng)前第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁

31

IDT72V263/273/283/293/103/113 3.3V HIGH DENSITY SUPERSYNC IITM NARROW BUS FIFO

8K x 18, 16K x 9/18, 32K x 9/18, 64K x 9/18, 128K x 9/18, 256K x 9/18, 512K x9

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

IDT72V223/233/243/253/263/273/283/293 3.3V HIGH DENSITY SUPERSYNC IITM NARROW BUS FIFO

512 x 18, 1K x 9/18, 2K x 9/18, 4K x 9/18, 8K x 9/18, 16K x 9/18, 32K x 9/18, 64K x 9/18, 128K x 9

FEBRUARY 11, 2009

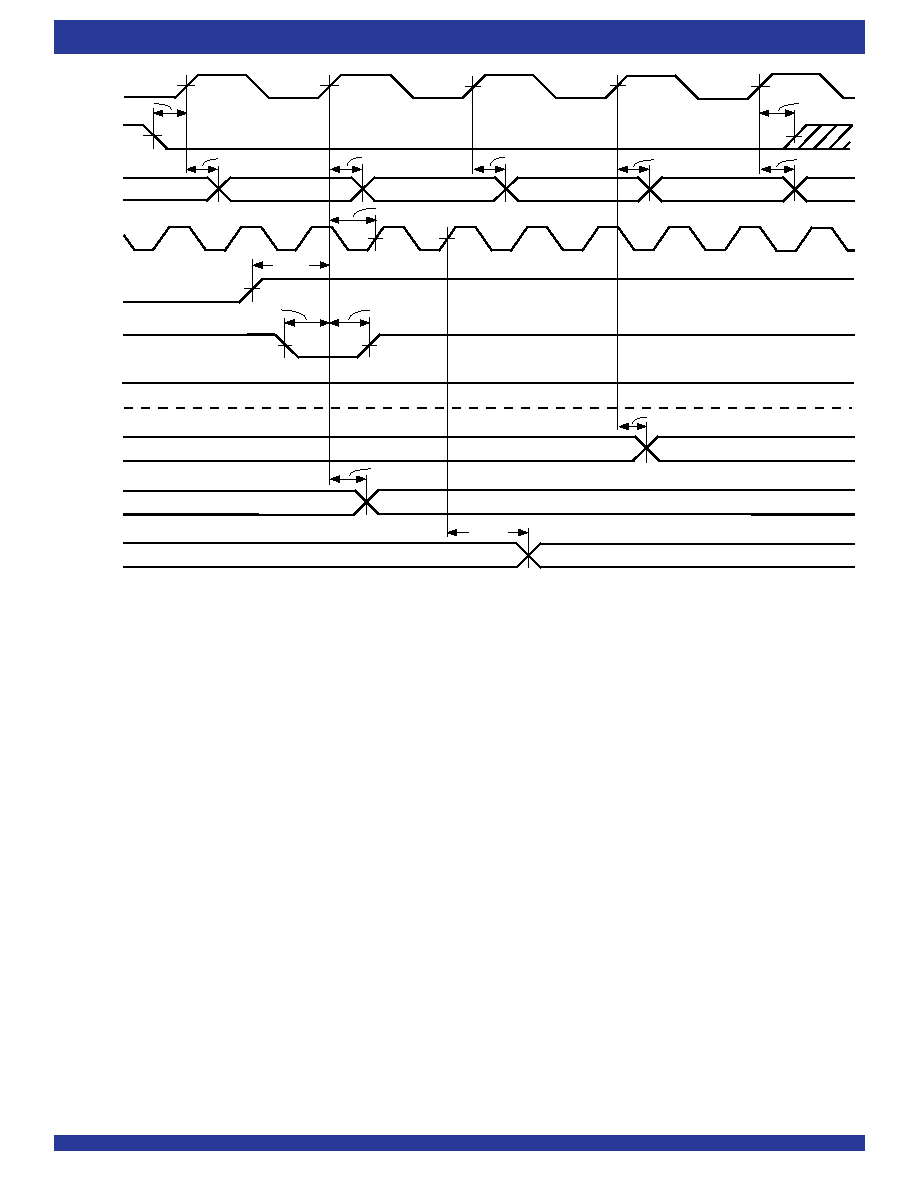

tRTS

tENH

4666 drw16

tA

tENS

Wx

WCLK

RCLK

REN

RT

EF(1)

PAF

HF

PAE

Q0 - Qn

tSKEW2

12

1

W3(3)

tPAFS

tHF

tPAES

Wx+1

2

W4

WEN

tENS

tENH

tA

3

tA

W1(3)

W2(3)

NOTES:

1. If the part is empty at the point of Retransmit, the Empty Flag (

EF) will be updated based on RCLK (Retransmit clock cycle). Valid data will also appear on the output.

2.

OE = LOW: enables data to be read on outputs Q0-Qn.

3. W1 = first word written to the FIFO after Master Reset, W2 = second word written to the FIFO after Master Reset.

4. No more than D - 2 may be written to the FIFO between Reset (Master or Partial) and Retransmit setup. Therefore,

FF will be HIGH throughout the Retransmit setup procedure.

If x18 Input or x18 Output bus Width is selected, D = 512 for the IDT72V223, 1,024 for the IDT72V233, 2,048 for the IDT72V243, 4,096 for the IDT72V253, 8,192 for the IDT72V263,

16,384 for the IDT72V273, 32,768 for the IDT72V283 and 65,536 for the IDT72V293.

If both x9 Input and x9 Output bus Widths are selected, D = 1,024 for the IDT72V223, 2,048 for the IDT72V233, 4,096 for the IDT72V243, 8,192 for the IDT72V253, 16,384

for the IDT72V263, 32,768 for the IDT72V273, 65,536 for the IDT72V283 and 131,072 for the IDT72V293.

5. There must be at least two words written to and read from the FIFO before a Retransmit operation can be invoked.

6. RM is set LOW during

MRS.

Figure 13. Zero Latency Retransmit Timing (IDT Standard Mode)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LT1739CFE#TRPBF | IC AMP XDSL LINE DRV DUAL20TSSOP |

| LT1739CFE#TR | IC AMP XDSL LINE DRV DUAL20TSSOP |

| MS27497T12F35P | CONN RCPT 22POS WALL MNT W/PINS |

| IDT72V231L15PFGI | IC FIFO SYNC 2048X9 15NS 32-TQFP |

| LTC1385ISW#PBF | IC TXRX 3.3V EIA/TIA-562 18-SOIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT72V223L7-5PFI | 功能描述:IC FIFO 512X18 7-5NS 80QFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72V225L10PF | 功能描述:IC FIFO SYNC 1024X18 10NS 64TQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72V225L10PF8 | 功能描述:IC FIFO SYNC 1024X18 10NS 64TQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問時間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤 其它名稱:72225LB10TF |

| IDT72V225L10PFG | 功能描述:IC FIFO SYNC 1024X18 10NS 64TQFP RoHS:是 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72V225L10PFG8 | 功能描述:IC FIFO SYNC 1024X18 10NS 64TQFP RoHS:是 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問時間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤 其它名稱:72225LB10TF |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。