- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄10107 > IDT72V215L15TF8 (IDT, Integrated Device Technology Inc)IC FIFO SYNC 512X18 15NS 64STQFP PDF資料下載

參數(shù)資料

| 型號(hào): | IDT72V215L15TF8 |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁(yè)數(shù): | 16/25頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC FIFO SYNC 512X18 15NS 64STQFP |

| 標(biāo)準(zhǔn)包裝: | 1,250 |

| 系列: | 72V |

| 功能: | 同步 |

| 存儲(chǔ)容量: | 9.2K(512 x 18) |

| 數(shù)據(jù)速率: | 67MHz |

| 訪問(wèn)時(shí)間: | 15ns |

| 電源電壓: | 3 V ~ 3.6 V |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 64-LQFP |

| 供應(yīng)商設(shè)備封裝: | 64-TQFP(10x10) |

| 包裝: | 帶卷 (TR) |

| 其它名稱: | 72V215L15TF8 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)當(dāng)前第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)

23

IDT72V205/72V215/72V225/72V235/72V245 3.3V CMOS SyncFIFOTM

256 x 18, 512 x 18, 1,024 x 18, 2,048 x 18 and 4,096 x 18

COMMERCIALANDINDUSTRIAL

TEMPERATURERANGES

MARCH 2013

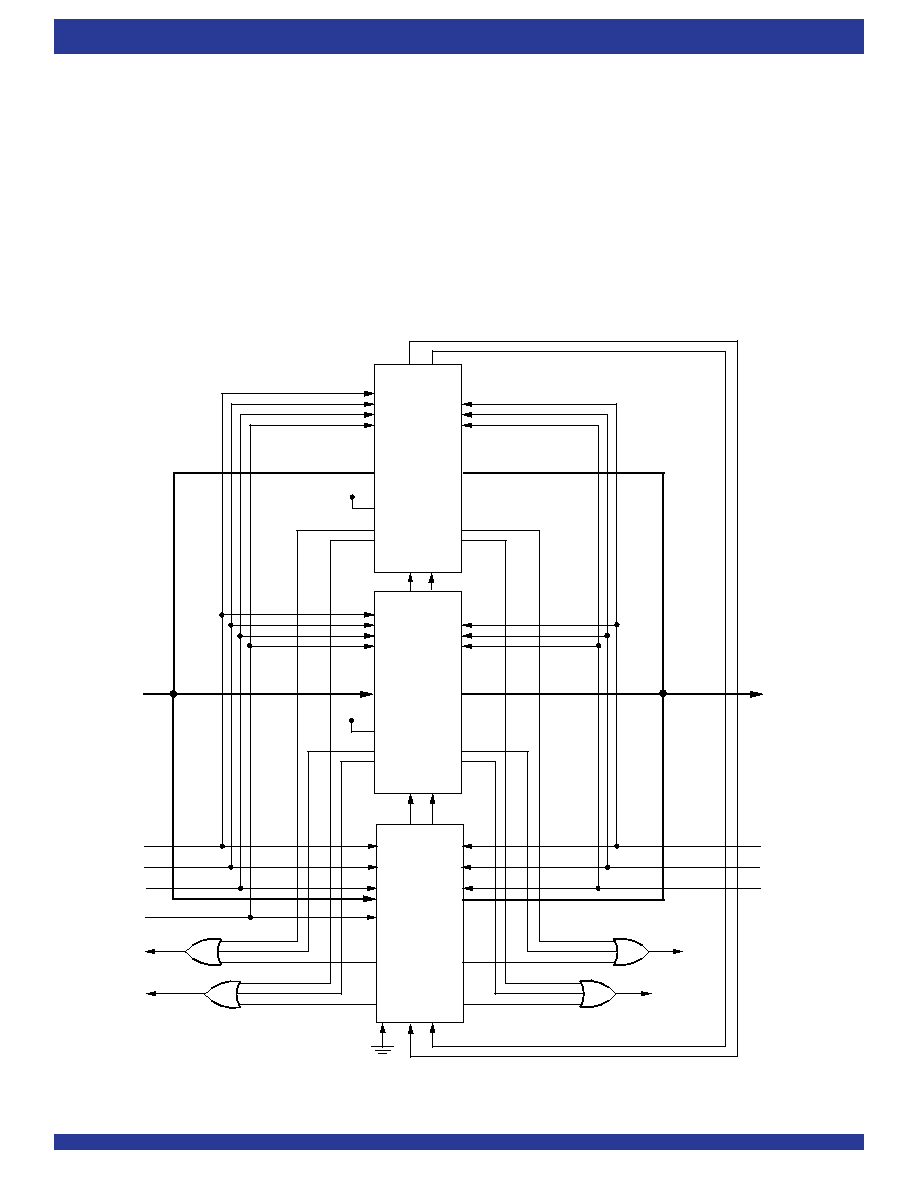

Figure 30. Block Diagram of 768 x 18, 1,536 x 18, 3,072 x 18, 6,144 x 18, 12,288 x 18 Synchronous

FIFO Memory With Programmable Flags used in Depth Expansion Configuration

LOAD

WRITE CLOCK

READ CLOCK

READ ENABLE

OUTPUT ENABLE

DATA IN

DATA OUT

RESET

IDT

72V205

72V215

72V225

72V235

72V245

WXO

WXI

RXO

RXI

FIRST LOAD (

FL)

FL

Vcc

WXO

WXI

RXO

RXI

WXO

WXI

RXO

RXI

IDT

72V205

72V215

72V225

72V235

72V245

IDT

72V205

72V215

72V225

72V235

72V245

FF/IR

PAF

EF/OR

PAE

FF/IR

PAF

EF/OR

PAE

FF/IR

PAF

EF/OR

PAE

EF/OR

PAE

FF/IR

PAF

4294 drw 30

RCLK

REN

OE

WCLK

WEN

RS

FL

RCLK

REN

OE

WCLK

WEN

RS

RCLK

REN

OE

WCLK

WEN

RS

LD

Dn

Qn

Dn

Qn

Dn

Qn

LD

DEPTH EXPANSION CONFIGURATION — DAISY CHAIN TECHNIQUE

(WITH PROGRAMMABLE FLAGS)

These devices can easily be adapted to applications requiring more than

256/512/1,024/2,048/4,096 words of buffering. Figure 30 shows Depth

Expansion using three IDT72V205/72V215/72V225/72V235/72V245s.

Maximumdepthislimitedonlybysignalloading.

Followthesesteps:

1. The first device must be designated by grounding the First Load (FL)

control input.

2. All other devices must have FL in the HIGH state.

3. The Write Expansion Out (WXO) pin of each device must be tied to

the Write Expansion In (WXI) pin of the next device. See Figure 30.

4. The Read Expansion Out (RXO) pin of each device must be tied to the

Read Expansion In (RXI) pin of the next device. See Figure 30.

5. All Load (LD) pins are tied together.

6. The Half-Full Flag (HF) is not available in this Depth Expansion

Configuration.

7. EF, FF, PAE, and PAF are created with composite flags by ORing

together every respective flags for monitoring. The composite PAE

and PAF flags are not precise.

8. In Daisy Chain mode, the flag outputs are single register-buffered and

thepartialflagsareinasynchronoustimingmode.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MS3101E16S-6S | CONN RCPT 3POS FREE HNG W/SCKT |

| IDT72225LB25TF8 | IC FIFO 1024X18 SYNC 25NS 64TQFP |

| MS3106F28-1P | CONN PLUG 9POS STRAIGHT W/PINS |

| MS3101A24-27P | CONN RCPT 7POS FREE HNG W/PINS |

| IDT72215LB25TFI8 | IC FIFO 512X18 SYNC 25NS 64QFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT72V215L15TFGI | 制造商:Integrated Device Technology Inc 功能描述:IC FIFO SYNC 512X18 15NS 64STQFP |

| IDT72V215L15TFGI8 | 制造商:Integrated Device Technology Inc 功能描述:IC FIFO SYNC 512X18 15NS 64STQFP |

| IDT72V215L15TFI | 功能描述:IC FIFO SYNC 512X18 15NS 64STQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲(chǔ)容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤(pán) 其它名稱:72225LB10TF |

| IDT72V215L15TFI8 | 功能描述:IC FIFO SYNC 512X18 15NS 64STQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲(chǔ)容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤(pán) 其它名稱:72225LB10TF |

| IDT72V215L20PF | 功能描述:IC FIFO SYNC 512X18 20NS 64-TQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲(chǔ)容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤(pán) 其它名稱:72225LB10TF |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。