- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄10108 > IDT72V211L20PF (IDT, Integrated Device Technology Inc)IC FIFO SYNC 512X9 20NS 32-TQFP PDF資料下載

參數(shù)資料

| 型號(hào): | IDT72V211L20PF |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁(yè)數(shù): | 3/14頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC FIFO SYNC 512X9 20NS 32-TQFP |

| 標(biāo)準(zhǔn)包裝: | 50 |

| 系列: | 72V |

| 功能: | 同步 |

| 存儲(chǔ)容量: | 4.6K(512 x 9) |

| 訪問(wèn)時(shí)間: | 20ns |

| 電源電壓: | 3 V ~ 3.6 V |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類(lèi)型: | 表面貼裝 |

| 封裝/外殼: | 32-LQFP |

| 供應(yīng)商設(shè)備封裝: | 32-TQFP(7x7) |

| 包裝: | 托盤(pán) |

| 其它名稱: | 72V211L20PF |

第1頁(yè)第2頁(yè)當(dāng)前第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)

11

IDT72V201/72V211/72V221/72V231/72V241/72V251 3.3V CMOS SyncFIFO

256 x 9, 512 x 9, 1,024 x 9, 2,048 x 9, 4,096 x 9 and 8,192 x 9

COMMERCIALANDINDUSTRIAL

TEMPERATURERANGES

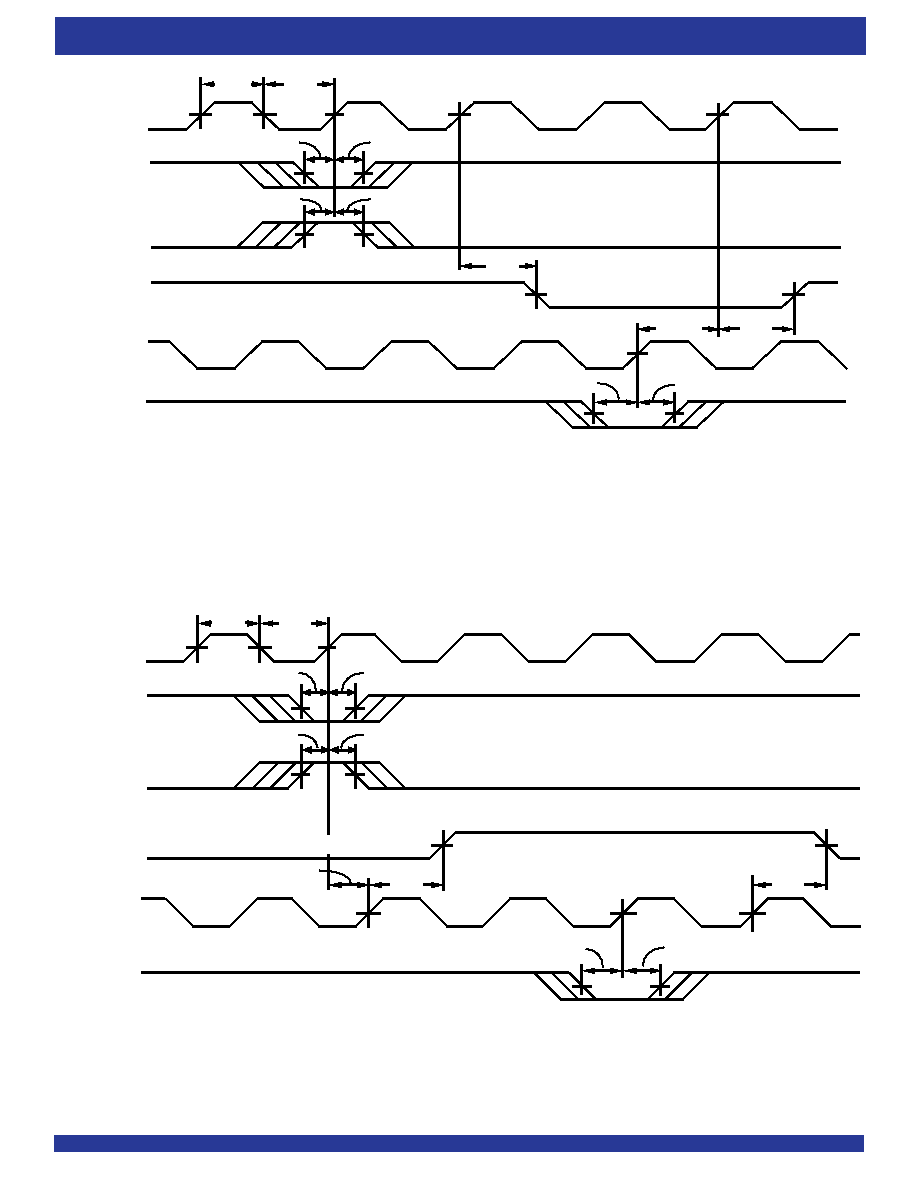

NOTES:

1. m = PAF offset.

2. 256 - m words in FIFO for IDT72V201, 512 - m words for IDT72V211, 1,024 - m words for IDT72V221, 2,048 - m words for IDT72V231, 4,096 - m words for IDT72V241, 8,192 - m

words for IDT72V251.

3. tSKEW2 is the minimum time between a rising RCLK edge and a rising WCLK edge for PAF to change during that clock cycle. If the time between the rising edge of RCLK and

the rising edge of WCLK is less than tSKEW2, then PAF may not change state until the next WCLK rising edge.

4. If a write is performed on this rising edge of the write clock, there will be Full - (m-1) words in the FIFO when PAF goes LOW.

NOTES:

1. n = PAE offset.

2. tSKEW2 is the minimum time between a rising WCLK edge and a rising RCLK edge for PAE to change during that clock cycle. If the time between the rising edge of WCLK and

the rising edge of RCLK is less than tSKEW2, then PAE may not change state until the next RCLK rising edge.

3. If a read is performed on this rising edge of the read clock, there will be Empty + (n-1) words in the FIFO when PAE goes LOW.

Figure 11. Programmable Empty Flag Timing

Figure 10. Programmable Full Flag Timing

tENS

tENH

tENS

tENH

tENS

tENH

WCLK

WEN1

WEN2

(If Applicable)

PAF

RCLK

REN1,

REN2

(4)

(1)

tPAF

Full - (m + 1) words in FIFO

Full - m words in FIFO

(2)

tCLKH

tCLKL

tSKEW2

(3)

tPAF

4092 drw12

WCLK

WEN1

WEN2

PAE

RCLK

REN1,

REN2

tENS

tENH

tENS

tENH

tSKEW2

(2)

tENS

tENH

(If Applicable)

tPAE

(3)

(1)

n words in FIFO

n + 1 words in FIFO

tCLKH

tCLKL

4092 drw13

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD7880BR | IC ADC 12BIT LC2MOS 5V LP 24SOIC |

| D38999/26FD5PD | CONN PLUG 5POS STRAIGHT W/PINS |

| AD977AR-REEL | IC ADC 16BIT 100KSPS 20-SOIC |

| VE-23T-IW-F2 | CONVERTER MOD DC/DC 6.5V 100W |

| LTC1606AISW | IC ADC 16BIT 5V SAMPLING 28SOIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT72V211L20PF8 | 功能描述:IC FIFO SYNC 512X9 20NS 32-TQFP RoHS:否 類(lèi)別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲(chǔ)容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類(lèi)型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤(pán) 其它名稱:72225LB10TF |

| IDT72V215L10PF | 功能描述:IC FIFO SYNC 512X18 10NS 64-TQFP RoHS:否 類(lèi)別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲(chǔ)容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類(lèi)型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤(pán) 其它名稱:72225LB10TF |

| IDT72V215L10PF8 | 功能描述:IC FIFO SYNC 512X18 10NS 64-TQFP RoHS:否 類(lèi)別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲(chǔ)容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類(lèi)型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤(pán) 其它名稱:72225LB10TF |

| IDT72V215L10TF | 功能描述:IC FIFO SYNC 512X18 10NS 64STQFP RoHS:否 類(lèi)別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲(chǔ)容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類(lèi)型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤(pán) 其它名稱:72225LB10TF |

| IDT72V215L10TF8 | 功能描述:IC FIFO SYNC 512X18 10NS 64STQFP RoHS:否 類(lèi)別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:80 系列:7200 功能:同步 存儲(chǔ)容量:18.4K(1K x 18) 數(shù)據(jù)速率:- 訪問(wèn)時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類(lèi)型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(10x10) 包裝:托盤(pán) 其它名稱:72225LB10TF |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。