- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4580 > IDT72T6360L7-5BB (IDT, Integrated Device Technology Inc)IC FLOW-CTRL 48BIT 7-5NS 324-BGA PDF資料下載

參數(shù)資料

| 型號(hào): | IDT72T6360L7-5BB |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁(yè)數(shù): | 29/51頁(yè) |

| 文件大小: | 0K |

| 描述: | IC FLOW-CTRL 48BIT 7-5NS 324-BGA |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 類型: | 連續(xù)流量控制 |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 324-BGA |

| 供應(yīng)商設(shè)備封裝: | 324-PBGA(19x19) |

| 包裝: | 托盤 |

| 其它名稱: | 72T6360L7-5BB |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)當(dāng)前第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)

35

IDT72T6360 2.5V, SEQUENTIAL FLOW-CONTROL DEVICE

x9, x18, x36 BIT WIDE CONFIGURATION

COMMERCIALANDINDUSTRIAL

TEMPERATURERANGES

FEBRUARY 10, 2009

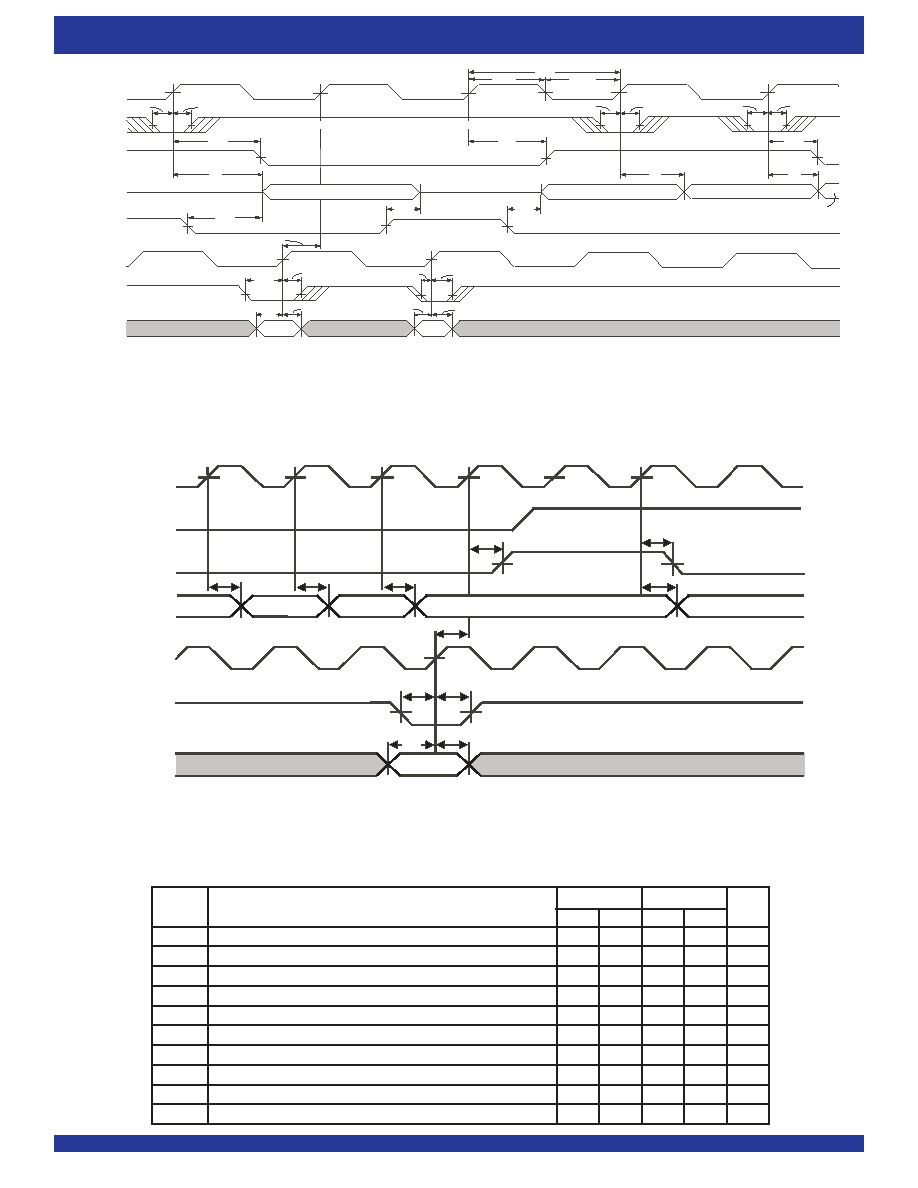

Figure 10. Empty Boundary - IDT Standard Mode

NO OPERATION

RCLK

REN

6357 drw24

EF

tCLK

tCLKH

tCLKL

tENH

tREF

tA

tOE

Q[35:0]

OE

WCLK

(1)

tSKEW1

WEN

D[35:0]

tENS

tENH

tDS

tDH

Word 0

1

2

tOLZ

NO OPERATION

Last Word

Word 0

tENS

tENH

tDS

tDH

tOHZ

Last Word

tREF

tENH

tENS

tA

tREF

tENS

tENH

Word 1

NOTES:

1. tSKEW1 is the minimum time between a rising WCLK edge and a rising RCLK edge to guarantee that

EF will go HIGH after one RCLK cycle (plus tREFs). If tSKEW1 is

not met, then

EF de-assertion may be delayed one extra RCLK cycle.

2. Settings:

RCS = LOW, WCS = LOW, BM[3:0] = 1000, FWFT = LOW, ASYR = HIGH, and ASYW = HIGH.

6ns

7-5ns

Symbol

Parameter

Min.

Max.

Min.

Max.

Unit

tCLK

Clock Cycle Time

6

—

7.5

—

ns

tCLKH

Clock High Time

2.7

—

3.5

—

ns

tCLKL

Clock Low Time

2.7

—

3.5

—

ns

tDS

DataSetupTime

2

—

2.5

—

ns

tDH

Data Hold Time

0.5

—

0.5

—

ns

tENS

Enable Setup Time

2

—

2.5

—

ns

tENH

Enable Hold Time

0.5

—

0.5

—

ns

tA

Data Access Time

1

4

1

5

ns

tREFs

Read Clock to Synchronous

EF/OR

—4

—

5

ns

tSKEW1

Skew time between RCLK and WCLK for

EF/OR and FF/IR in SDR

4

—

5

—

ns

Figure 11. Empty Boundary - FWFT Mode

12

3

tA

Last Word - 2

RCLK

REN

OR

WCLK

6357 drw25

WEN

D[35:0]

tENS tENH

Q[35:0]

Word 0

tDS

tDH

Last Word - 3

tA

Last Word - 1

tREFs

tSKEW1

Last Word

tA

Word 0

tREFs

NOTES:

1. tSKEW1 is the minimum time between a rising WCLK edge and a rising RCLK edge to guarantee that

EF will go HIGH after one RCLK cycle (plus tREFs).

If tSKEW1 is not met, then

EF de-assertion may be delayed one extra RCLK cycle.

2. Settings:

OE = LOW, RCS = LOW, WCS = LOW, BM[3:0] = 1000, FWFT = HIGH, ASYR = HIGH, and ASYW = HIGH.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LT1528CQ | IC REG LDO 3.3V/ADJ 3A DDPAK-5 |

| ASM25DRKF | CONN EDGECARD 50POS DIP .156 SLD |

| ACC30DRAI-S734 | CONN EDGECARD 60POS .100 R/A PCB |

| HCC60DRYN-S13 | CONN EDGECARD 120PS .100 EXTEND |

| HCC60DRYH-S13 | CONN EDGECARD 120PS .100 EXTEND |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT72T6360L7-5BBI | 功能描述:IC FLOW-CTRL 48BIT 7-5NS 324-BGA RoHS:否 類別:集成電路 (IC) >> 專用 IC 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT72T6480L10BB | 功能描述:IC FLOW-CTRL 48BIT 10NS 324-BGA RoHS:否 類別:集成電路 (IC) >> 專用 IC 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT72T6480L10BBI | 功能描述:IC FLOW-CTRL 48BIT 10NS 324-BGA RoHS:否 類別:集成電路 (IC) >> 專用 IC 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT72T6480L7-5BB | 功能描述:IC FLOW-CTRL 48BIT 7-5NS 324-BGA RoHS:否 類別:集成電路 (IC) >> 專用 IC 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT72T6480L7-5BBG | 功能描述:IC FLOW-CTRL 48BIT 7-5NS 324-BGA RoHS:是 類別:集成電路 (IC) >> 專用 IC 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。