- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377254 > IDT7006S35PFB (INTEGRATED DEVICE TECHNOLOGY INC) Single Synchronous Buck PWM Controller; Package: SOIC; No of Pins: 8; Container: Tape & Reel PDF資料下載

參數(shù)資料

| 型號(hào): | IDT7006S35PFB |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | DRAM |

| 英文描述: | Single Synchronous Buck PWM Controller; Package: SOIC; No of Pins: 8; Container: Tape & Reel |

| 中文描述: | 16K X 8 DUAL-PORT SRAM, 35 ns, PQFP64 |

| 封裝: | 14 X 14 MM, 1.40 MM HEIGHT, TQFP-64 |

| 文件頁數(shù): | 9/20頁 |

| 文件大小: | 263K |

| 代理商: | IDT7006S35PFB |

IDT7006S/L

HIGH-SPEED 16K x 8 DUAL-PORT STATIC RAM

MILITARY AND COMMERCIAL TEMPERATURE RANGES

6.07

9

IDT7006X15

Com'l. Only

Min.

IDT7006X17

Com'l. Only

Min.

IDT7006X20

IDT7006X25

Symbol

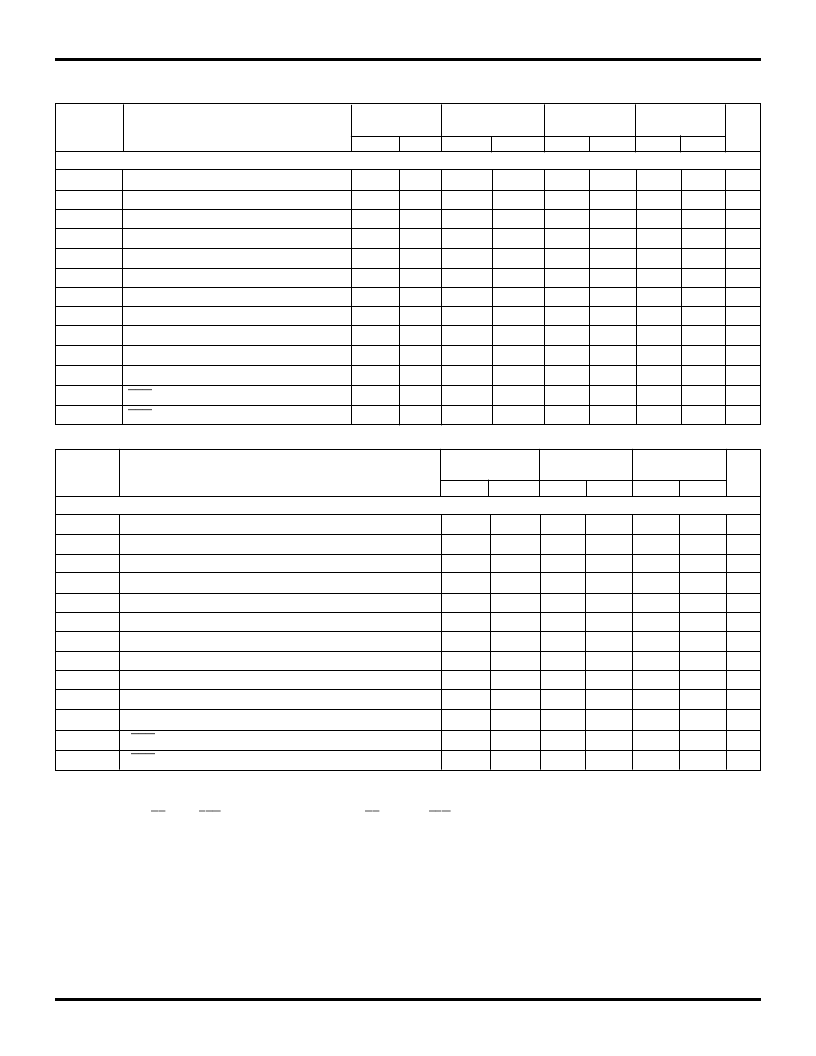

WRITE CYCLE

t

WC

t

EW

t

AW

t

AS

t

WP

t

WR

t

DW

t

HZ

Parameter

Max.

Max.

Min.

Max.

Min.

Max.

Unit

Write Cycle Time

Chip Enable to End-of-Write

(3)

Address Valid to End-of-Write

Address Set-up Time

(3)

Write Pulse Width

Write Recovery Time

Data Valid to End-of-Write

Output High-Z Time

(1, 2)

Data Hold Time

(4)

Write Enable to Output in High-Z

(1, 2)

Output Active from End-of-Write

(1, 2, 4)

15

12

12

0

12

0

10

—

—

—

—

—

—

—

—

10

17

12

12

0

12

0

10

—

—

—

—

—

—

—

—

10

20

15

15

0

15

0

15

—

—

—

—

—

—

—

—

12

25

20

20

0

20

0

15

—

—

—

—

—

—

—

—

15

ns

ns

ns

ns

ns

ns

ns

ns

t

DH

0

—

0

—

0

—

0

—

ns

t

WZ

t

OW

—

0

—

—

—

0

—

—

—

0

12

—

—

0

15

—

ns

ns

t

SWRD

SEM

Flag Write to Read Time

5

—

5

—

5

—

5

—

ns

t

SPS

SEM

Flag Contention Window

5

—

5

—

5

—

5

—

ns

IDT7006X35

IDT7006X55

IDT7006X70

Mil. Only

Min.

Symbol

WRITE CYCLE

t

WC

t

EW

t

AW

t

AS

t

WP

t

WR

t

DW

t

HZ

t

DH

Parameter

Min.

Max.

Min.

Max.

Max.

Unit

Write Cycle Time

Chip Enable to End-of-Write

(3)

Address Valid to End-of-Write

Address Set-up Time

(3)

Write Pulse Width

Write Recovery Time

Data Valid to End-of-Write

Output High-Z Time

(1, 2)

Data Hold Time

(4)

Write Enable to Output in High-Z

(1, 2)

Output Active from End-of-Write

(1, 2, 4)

SEM

Flag Write to Read Time

35

30

30

0

25

0

15

—

0

—

—

—

—

—

—

—

15

—

55

45

45

0

40

0

30

—

0

—

—

—

—

—

—

—

25

—

70

50

50

0

50

0

40

—

0

—

—

—

—

—

—

—

30

—

ns

ns

ns

ns

ns

ns

ns

ns

ns

t

WZ

—

15

—

25

—

30

ns

t

OW

t

SWRD

0

5

—

—

0

5

—

—

0

5

—

—

ns

ns

t

SPS

SEM

Flag Contention Window

5

—

5

—

5

—

ns

NOTES:

1. Transition is measured

±

500mV from Low or High-impedance voltage with Output Test Load (Figure 2).

2. This parameter is guaranteed by device characterization, but is not production tested.

3. To access RAM,

CE

= V

IL

,

SEM

= V

IH

. To access semaphore,

CE

= V

IH

and

SEM

= V

IL

. Either condition must be valid for the entire t

EW

time.

4. The specification for t

DH

must be met by the device supplying write data to the RAM under all operating conditions. Although t

DH

and t

OW

values will vary

over voltage and temperature, the actual t

DH

will always be smaller than the actual t

OW

.

5. "X" in part numbers indicates power rating (S or L).

2739 tbl 14

AC ELECTRICAL CHARACTERISTICS OVER THE

OPERATING TEMPERATURE AND SUPPLY VOLTAGE RANGE

(5)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT7006S55G | Single Synchronous Buck PWM Controller |

| IDT7006S55GB | Single Synchronous Buck PWM Controller; Package: SOIC; No of Pins: 8; Container: Rail |

| IDT7006S55J | Single Synchronous Buck PWM Controller |

| IDT7006S55PF | Single Synchronous Buck PWM Controller; Package: SOIC; No of Pins: 8; Container: Tape & Reel |

| IDT7006S55PFB | Single Synchronous Buck PWM Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT7006S35XL | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 Dual-Port SRAM |

| IDT7006S35XLB | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 Dual-Port SRAM |

| IDT7006S45F | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 Dual-Port SRAM |

| IDT7006S45FB | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 Dual-Port SRAM |

| IDT7006S45G | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 Dual-Port SRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。