- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377132 > IDT49ALVCH16823PA (Integrated Device Technology, Inc.) 3.3V CMOS 18-BIT BUS-INTERFACE FLIPFLOP WITH 3-STATE OUTPUTS AND BUS-HOLD PDF資料下載

參數(shù)資料

| 型號: | IDT49ALVCH16823PA |

| 廠商: | Integrated Device Technology, Inc. |

| 英文描述: | 3.3V CMOS 18-BIT BUS-INTERFACE FLIPFLOP WITH 3-STATE OUTPUTS AND BUS-HOLD |

| 中文描述: | 3.3V的CMOS 18位總線接口觸發(fā)器具有三態(tài)輸出和總線狀態(tài)保持 |

| 文件頁數(shù): | 2/7頁 |

| 文件大小: | 79K |

| 代理商: | IDT49ALVCH16823PA |

INDUSTRIAL TEMPERATURE RANGE

2

IDT74ALVCH16823

3.3V CMOS 18-BIT BUS-INTERFACE FLIP-FLOP WITH 3-STATE OUTPUTS

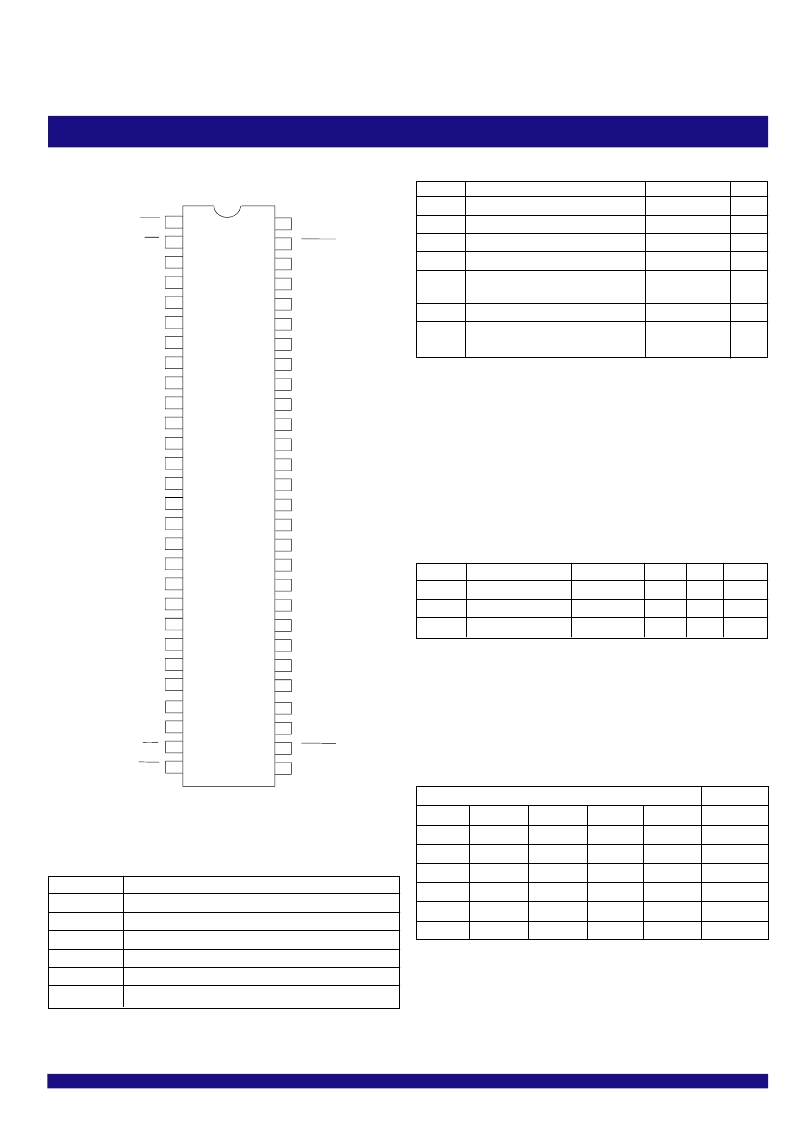

TSSOP

TOP VIEW

PIN CONFIGURATION

NOTE:

1. As applicable to the device type.

Symbol

C

IN

C

OUT

C

OUT

Parameter

(1)

Input Capacitance

Output Capacitance

I/O Port Capacitance

Conditions

V

IN

= 0V

V

OUT

= 0V

V

IN

= 0V

Typ.

5

7

7

Max.

7

9

9

Unit

pF

pF

pF

CAPACITANCE

(T

A

= +25°C, F = 1.0MHz)

Symbol

V

TERM

(2)

V

TERM

(3)

T

STG

I

OUT

I

IK

Description

Max

Unit

V

V

°C

mA

mA

Termnal Voltage with Respect to GND

Termnal Voltage with Respect to GND

Storage Temperature

DC Output Current

Continuous Clamp Current,

V

I

< 0 or V

I

> V

CC

Continuous Clamp Current, V

O

< 0

Continuous Current through each

V

CC

or GND

–0.5 to +4.6

–0.5 to V

CC

+0.5

–65 to +150

–50 to +50

±50

I

OK

I

CC

I

SS

–50

±100

mA

mA

ABSOLUTE MAX IMUM RATINGS

(1)

NOTES:

1. Stresses greater than those listed under ABSOLUTE MAXIMUMRATINGS may cause

permanent damage to the device. This is a stress rating only and functional operation

of the device at these or any other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to absolute maximumrating

conditions for extended periods may affect reliability.

2. V

CC

termnals.

3. All termnals except V

CC

.

1

CLR

1

OE

1

Q

1

GND

1

Q

2

1

Q

3

V

CC

1

Q

4

1

Q

5

GND

1

Q

6

1

Q

7

1

Q

8

1

Q

9

2

Q

2

2

Q

3

GND

2

Q

4

2

Q

5

2

Q

6

V

CC

2

Q

7

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

48

49

50

51

52

53

54

55

56

1

1

CLK

1

CLKEN

1

D

1

GND

1

D

2

1

D

3

V

CC

1

D

4

1

D

5

1

D

6

1

D

7

1

D

8

1

D

9

GND

2

D

2

2

D

3

2

D

4

2

D

5

GND

2

D

6

2

D

7

2

D

8

GND

2

Q

9

2

OE

2

CLR

25

26

27

28

32

31

30

29

GND

2

D

9

2

CLKEN

2

CLK

2

Q

1

2

Q

8

V

CC

2

D

1

FUNCTION TABLE

(EACH 9-BIT FLIP-FLOP)

(1)

Inputs

xOE

xCLR

xCLKEN

L

L

X

L

H

L

L

H

L

L

H

L

L

H

H

H

X

X

NOTES:

1. H = HIGH Voltage Level

L = LOW Voltage Level

X = Dont Care

Z = High Impedance

↑

= LOW-to-HIGH transition

2. Output level before the indicated steady-state input conditions were established.

Output

xQx

L

H

L

Q

0

Q

0

Z

xCLK

X

↑

↑

L

X

X

xDx

X

H

L

X

X

X

(2)

(2)

Pin Names

xDx

xCLK

xCLKEN

xQx

xOE

xCLR

Description

Data Inputs

(1)

Clock Input

Clock Enable Inputs

3-State Outputs

3-State Output Enable Inputs

Clear Inputs

PIN DESCRIPTION

NOTE:

1. These pins have "Bus-Hold". All other pins are standard inputs, outputs, or I/Os.

相關PDF資料 |

PDF描述 |

|---|---|

| IDT61ALVCH16823PA | 3.3V CMOS 18-BIT BUS-INTERFACE FLIPFLOP WITH 3-STATE OUTPUTS AND BUS-HOLD |

| IDT62ALVCH16823PA | 3.3V CMOS 18-BIT BUS-INTERFACE FLIPFLOP WITH 3-STATE OUTPUTS AND BUS-HOLD |

| IDT63ALVCH16823PA | 3.3V CMOS 18-BIT BUS-INTERFACE FLIPFLOP WITH 3-STATE OUTPUTS AND BUS-HOLD |

| IDT64ALVCH16823PA | 3.3V CMOS 18-BIT BUS-INTERFACE FLIPFLOP WITH 3-STATE OUTPUTS AND BUS-HOLD |

| IDT65ALVCH16823PA | 3.3V CMOS 18-BIT BUS-INTERFACE FLIPFLOP WITH 3-STATE OUTPUTS AND BUS-HOLD |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| IDT49C25AD | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Four Distributed-Output Clock Driver |

| IDT49C25ADB | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Four Distributed-Output Clock Driver |

| IDT49C25AE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Four Distributed-Output Clock Driver |

| IDT49C25AEB | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Four Distributed-Output Clock Driver |

| IDT49C25AJ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Four Distributed-Output Clock Driver |

發(fā)布緊急采購,3分鐘左右您將得到回復。