- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360746 > ICS2572 User-Programmable Dual High-Performance Clock Generator PDF資料下載

參數(shù)資料

| 型號: | ICS2572 |

| 英文描述: | User-Programmable Dual High-Performance Clock Generator |

| 中文描述: | 用戶可編程雙路高性能時鐘發(fā)生器 |

| 文件頁數(shù): | 4/10頁 |

| 文件大?。?/td> | 144K |

| 代理商: | ICS2572 |

Observe that the internal shift register is “clocked” by a tran-

sition of FS3 data from “0” to “1.” If an extended sequence of

register loading is to be performed (such as a power-on initiali-

zation sequence), note that it is not necessary to implement the

50 millisecond delay between them. Simply repeat the se-

quence above as many times as desired. Writes to the FS port

will not be treated as frequency select data until up to 50

milliseconds have transpired since the last write. Note that FS0

and FS1 inputs are “don’t care.”

Data Description

Location Bits (L0-L4)

The first five bits after the start bit control the frequency

location to be re-programmed according to this table. The

rightmost bit (the LSB) of the five shown in each selection of

the table is the first one sent.

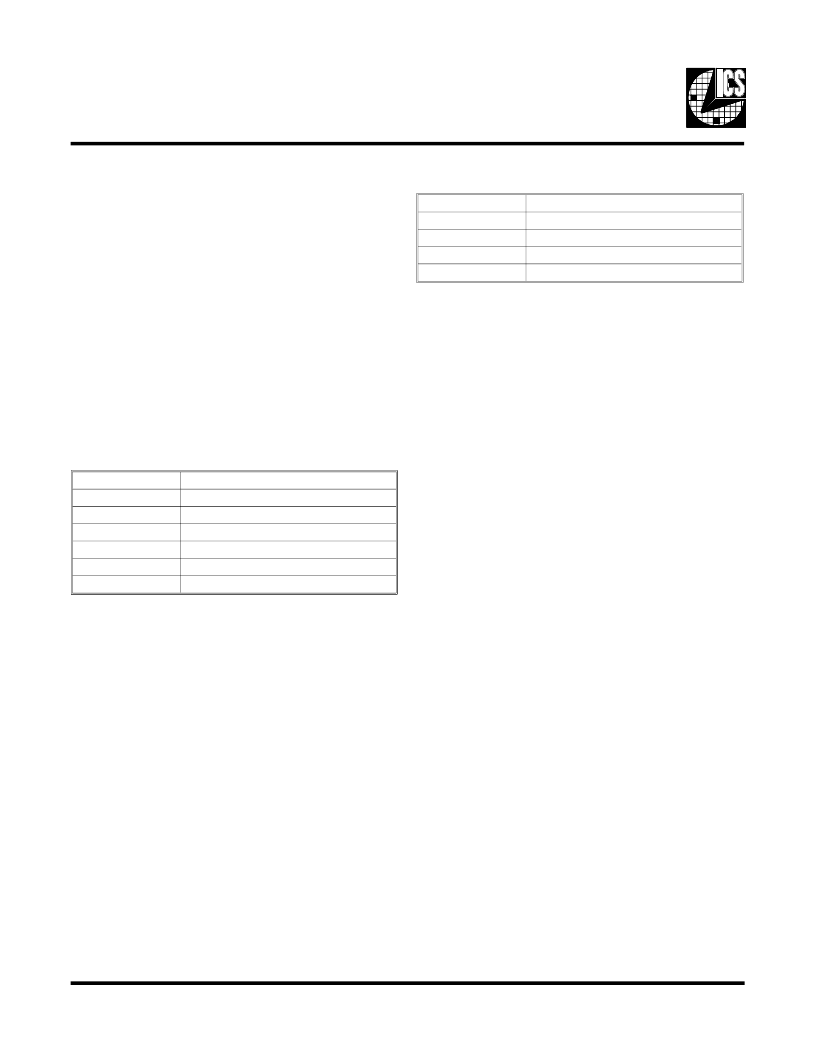

Table 1 - Location Bit Programming

L[4-0]

01100

01101

01110

01111

10010

10011

LOCATION

VCLK Address 12

VCLK Address 13

VCLK Address 14

VCLK Address 15

MCLK Address 2

MCLK Address 3

Feedback Set Bits (N0-N7)

These bits control the feedback divider setting for the location

to the value of these bits + 257. The least significant bit (N0)

is sent first.

Post-Divider Set Bits (D0-D1)

These bits control the post-divider setting for the location

specified according to this table. The least significant bit (D0)

is sent first.

Table 2 - Post-Divider Programming

D[1-0]

00

01

10

11

POST-DIVIDER

9

4

2

1

Read/Write* Control Bit

When set to a “0,” the ICS2572 shift register will transfer its

contents to the selected memory register at the completion of

the programming sequence outlined above.

When this bit is a “1,” the selected memory location will be

transferred to the shift register to permit a subsequent readback

of data. No modification of device memory will be performed.

To readback any location of memory, perform a “dummy”

write of data (complete with start and stop bits) to that location

but set the R/W* control bit (make it “1”). At the end of the

sequence (i.e., after the stop bits have been “clocked”), “clock-

ing” of the FS3 input 11 more times will output the data bits

only in the same sequence as above on the FS0 pin.

EXTFREQ Input

The EXTFREQ input allows an externally generated frequency

to be routed to the VCLK output pin under device program-

ming control. If the EXTFREQ bit is set (logic “1”) at the

selected address location (

VCLK addresses only

), the fre-

quency applied to the EXTFREQ input will be routed to the

VCLK output.

ICS2572

E-98

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ICS2572M | User-Programmable Dual High-Performance Clock Generator |

| ICS2572N | User-Programmable Dual High-Performance Clock Generator |

| ICS2595M-S04 | Video/Graphics Clock Generator |

| ICS2595N-S02 | Video/Graphics Clock Generator |

| ICS2595N-S04 | Video/Graphics Clock Generator |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ICS2572M | 制造商:ICS 制造商全稱:ICS 功能描述:User-Programmable Dual High-Performance Clock Generator |

| ICS2572M-A01 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral IC |

| ICS2572M-AXX | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral IC |

| ICS2572M-B01 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral IC |

| ICS2572M-BXX | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。