- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360707 > IBMN364164CT3C-68 x16 SDRAM PDF資料下載

參數(shù)資料

| 型號: | IBMN364164CT3C-68 |

| 英文描述: | x16 SDRAM |

| 中文描述: | x16內(nèi)存 |

| 文件頁數(shù): | 40/71頁 |

| 文件大小: | 1251K |

| 代理商: | IBMN364164CT3C-68 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁當(dāng)前第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁

IBMN364164

IBMN364404

64Mb Synchronous DRAM - Die Revision C

IBMN364804

IBM Corporation. All rights reserved.

Use is further subject to the provisions at the end of this document.

Page 40 of 71

19L3265.E35856B

1/01

AC Characteristics

(T

A

= 0 to +70

°

C, V

DD

= 3.3V

±

0.3V)

1. An initial pause of 200

μ

s, with DQM and CKE held high, is required after power-up. A Precharge All

Banks command must be given followed by a minimum of eight Auto (CBR) Refresh cycles before or after

the Mode Register Set operation.

2. The Transition time is measured between V

IH

and V

IL

(or between V

IL

and V

IH

)

3. In addition to meeting the transition rate specification, the clock and CKE must transit between V

IH

and V

IL

(or between V

IL

and V

IH

) in a monotonic manner.

4. Load Circuit A: AC timing tests have V

IL

= 0.4 V and V

IH

= 2.4 V with the timing referenced to the 1.40V

crossover point

5. Load Circuit A: AC measurements assume t

T

= 1.0ns.

6. Load Circuit B: AC timing tests have V

IL

= 0.8 V and V

IH

= 2.0 V with the timing referenced to the 1.40V

crossover point

7. Load Circuit B: AC measurements assume t

T

= 1.2ns.

.

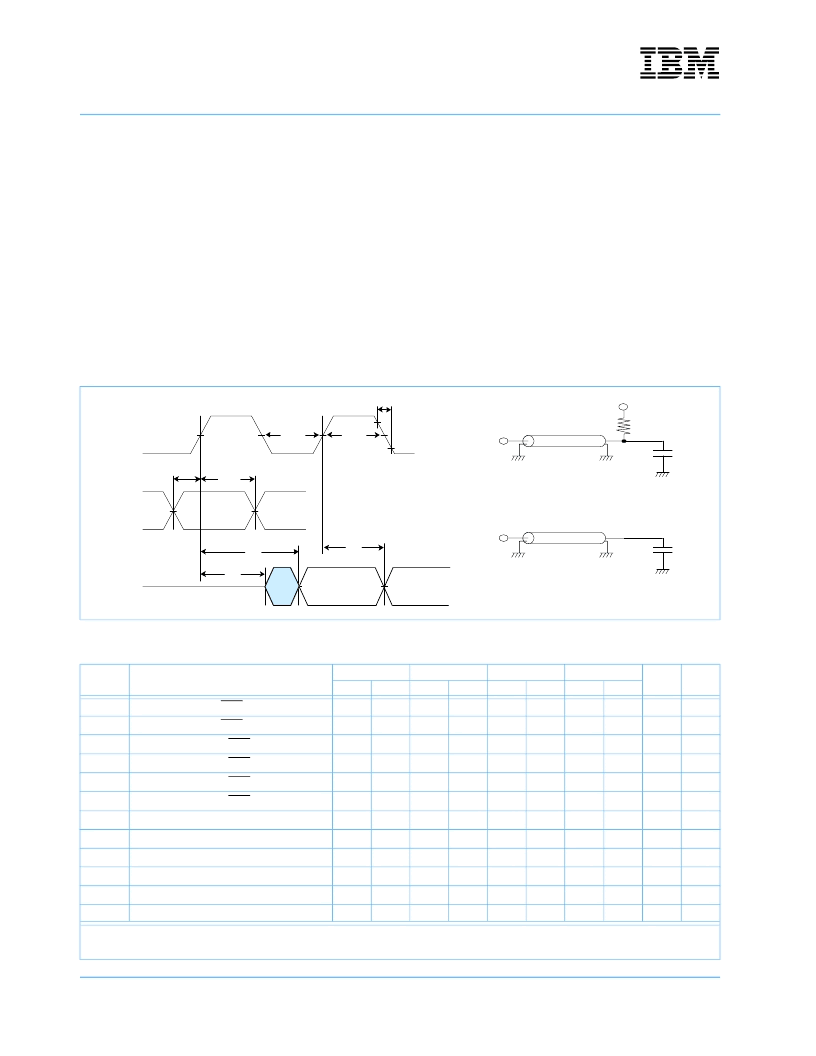

AC Output Diagrams

Clock and Clock Enable Parameters

Symbol

Parameter

-68

-75A

-260

-360

Units

Notes

Min.

6.67

—

—

—

—

—

Max.

1000

—

Min.

7.5

Max.

1000

Min.

10

Max.

1000

Min.

10

Max.

1000

t

CK3

t

CK2

t

AC3 (A)

t

AC2 (A)

t

AC3 (B)

t

AC2 (B)

t

CKH

t

CKL

t

CES

t

CEH

t

SB

t

T

Clock Cycle Time, CAS Latency = 3

ns

Clock Cycle Time, CAS Latency = 2

—

—

10

1000

15

1000

ns

Clock Access Time, CAS Latency = 3

6

—

—

—

—

—

—

—

—

—

—

—

—

—

ns

1

Clock Access Time, CAS Latency = 2

—

—

—

—

—

—

ns

1

Clock Access Time, CAS Latency = 3

—

5.4

—

6

—

6

ns

2

Clock Access Time, CAS Latency = 2

—

—

—

6

—

9

ns

2

Clock High Pulse Width

3

2.5

—

3

—

3

—

ns

Clock Low Pulse Width

3

2

1

2.5

—

3

—

3

—

ns

Clock Enable Set-up Time

1.5

0.8

—

—

2

1

—

—

2

1

—

—

ns

ns

Clock Enable Hold Time

Power down mode Entry Time

0

6.67

0

7.5

0

10

0

10

ns

Transition Time (Rise and Fall)

0.5

10

0.5

10

0.5

10

0.5

10

ns

1. Access time is measured at 1.4V. See AC Characteristics: notes 1, 2, 3, 4, 5 and load circuit A.

2. Access time is measured at 1.4V. See AC Characteristics: notes 1, 2, 3, 6, 7 and load circuit B.

Output

Input

Clock

t

OH

t

SETUP

t

HOLD

t

AC

t

LZ

1.4V

1.4V

V

IL

1.4V

t

T

Vtt = 1.4V

Output

50

50pF

Z

o

= 50

AC Output Load Circuit (A)

t

CKH

t

CKL

Output

50pF

Z

o

= 50

AC Output Load Circuit (B)

V

IH

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IBMN364164CT3C-75A | x16 SDRAM |

| IBMN364404CT3C-260 | x4 SDRAM |

| IBMN364404CT3C-360 | x4 SDRAM |

| IBMN364404CT3C-75A | x4 SDRAM |

| IBMN364804CT3C-260 | x8 SDRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IBMPPC403GAJC33C1 | 制造商:IBM 功能描述: |

| IBMPPC750CLGEQ4023 | 制造商:IBM 功能描述:MPU 750CL RISC 32BIT 90NM 400MHZ 1.15V/1.8V 278FCBGA - Trays |

| IBMPPC750CLGEQ5023 | 制造商:IBM Microelectronics 功能描述:MPU 750CL RISC 32BIT 90NM 500MHZ 1.15V/1.8V 278FCBGA - Trays |

| IBMPPC750CLGEQA033 | 制造商:IBM 功能描述:MPU 750CL RISC 32BIT 90NM 1GHZ 1.15V/1.8V 278FCBGA - Trays 制造商:IBM 功能描述:IBMIBMPPC750CLGEQA033 CPU PPC 750CL 1GHZ |

| IBN100 | 制造商:Hubbell Wiring Device-Kellems 功能描述:ICON, BLANK,BR,100PK |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。