- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385435 > HYS72T64000HU-3S-B (QIMONDA AG) 240-Pin unbuffered DDR2 SDRAM Modules PDF資料下載

參數(shù)資料

| 型號(hào): | HYS72T64000HU-3S-B |

| 廠商: | QIMONDA AG |

| 元件分類: | DRAM |

| 英文描述: | 240-Pin unbuffered DDR2 SDRAM Modules |

| 中文描述: | 64M X 72 DDR DRAM MODULE, 0.45 ns, DMA240 |

| 封裝: | GREEN, UDIMM-240 |

| 文件頁數(shù): | 3/87頁 |

| 文件大小: | 1723K |

| 代理商: | HYS72T64000HU-3S-B |

第1頁第2頁當(dāng)前第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁

Internet Data Sheet

Rev. 1.3, 2006-12

03292006-6GMD-RSFT

3

HYS[64/72]T[32/64/128]xx0HU-[25F/2.5/3/3S/3.7/5]-B

Unbuffered DDR2 SDRAM Module

1

Overview

This chapter gives an overview of the 240-Pin unbuffered DDR2 SDRAM Modules product family and describes its main

characteristics.

1.1

Features

Feature list and performance tables

240-Pin PC2–6400, PC2–5300, PC2–4200 and

PC2–3200 DDR2 SDRAM memory modules.

32M

×

64, 64M

×

64, 64M

×

72, 128M

×

64 and 128M

×

72

module organization and 32M

×

16, 64M

×

8 chip

organization

Standard Double-Data-Rate-Two Synchronous DRAMs

(DDR2 SDRAM) with a single + 1.8 V (± 0.1 V) power

supply

256MB, 512MB and 1GB modules built with 512-Mbit

DDR2 SDRAMs in P-TFBGA-84 and P-TFBGA-60

chipsize packages

All speed grades faster than DDR2–400 comply with

DDR2–400 timing specifications.

Programmable CAS Latencies (3, 4 and 5),

Burst Length (8 & 4) and Burst Type

Auto Refresh (CBR) and Self Refresh

Programmable self refresh rate via EMRS2 setting

Programmable partial array refresh via EMRS2 settings

Average Refresh Period 7.8

μ

s at a

T

CASE

lower than

85 °C, 3.9

μ

s between 85 °C and 95 °C.

DCC enabling via EMRS2 setting

All inputs and outputs SSTL_1.8 compatible

Off-Chip Driver Impedance Adjustment (OCD) and

On-Die Termination (ODT)

Serial Presence Detect with E

2

PROM

UDIMM Dimensions (nominal):

30 mm high, 133.35 mm wide

Based on standard reference layouts Raw Card “C”,

“D”,”E”,”F” and “G“

RoHS compliant products

1)

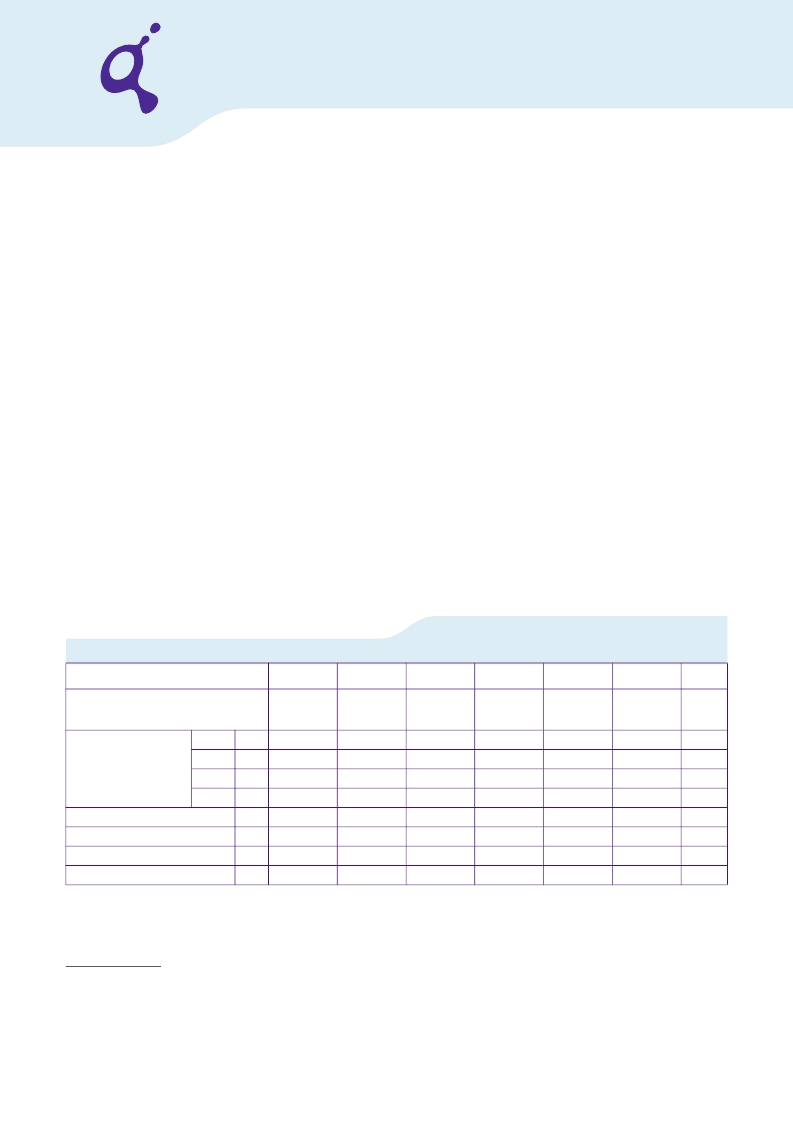

TABLE 1

Performance Table

1) RoHS Compliant Product: Restriction of the use of certain hazardous substances (RoHS) in electrical and electronic equipment as defined

in the directive 2002/95/EC issued by the European Parliament and of the Council of 27 January 2003. These substances include mercury,

lead, cadmium, hexavalent chromium, polybrominated biphenyls and polybrominated biphenyl ethers.

Product Type Speed Code

–25F

–2.5

–3

–3S

–3.7

–5

Unit

Speed Grade

PC2–6400

5–5–5

PC2–6400

6–6–6

PC2–5300

4–4–4

PC2–5300

5–5–5

PC2–4200

4–4–4

PC2–3200

3–3–3

—

Max. Clock Frequency

@CL6

f

CK6

400

400

266

200

12.5

12.5

45

57.5

400

333

266

200

15

15

45

60

—

333

333

200

12

12

45

57

—

333

266

200

15

15

45

60

—

266

266

200

15

15

45

60

—

200

200

200

15

15

40

55

MHz

MHz

MHz

MHz

ns

ns

ns

ns

@CL5

f

CK5

@CL4

f

CK4

@CL3

f

CK3

Min. RAS-CAS-Delay

Min. Row Precharge Time

Min. Row Active Time

Min. Row Cycle Time

t

RCD

t

RP

t

RAS

t

RC

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYS72T64000HU-5-B | 240-Pin unbuffered DDR2 SDRAM Modules |

| HYS72T128020HU-3.7-A | 240-Pin Unbuffered DDR2 SDRAM Modules |

| HYS72T128020HU-3-A | 240-Pin Unbuffered DDR2 SDRAM Modules |

| HYS72T128020HU-3S-A | 240-Pin Unbuffered DDR2 SDRAM Modules |

| HYS72T64000HU-3.7-A | 240-Pin Unbuffered DDR2 SDRAM Modules |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYS72T64000HU-5-A | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:240-Pin Unbuffered DDR2 SDRAM Modules |

| HYS72T64000HU-5-B | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:240-Pin unbuffered DDR2 SDRAM Modules |

| HYS72T64001GR | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:DDR2 Registered DIMM Modules |

| HYS72T64001GR-37-A | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:DDR2 Registered DIMM Modules |

| HYS72T64001GR-3-A | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:DDR2 Registered DIMM Modules |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。