- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370808 > HYS72D32500GR-7-B (INFINEON TECHNOLOGIES AG) Registered DDR SDRAM-Modules PDF資料下載

參數(shù)資料

| 型號: | HYS72D32500GR-7-B |

| 廠商: | INFINEON TECHNOLOGIES AG |

| 英文描述: | Registered DDR SDRAM-Modules |

| 中文描述: | 注冊DDR SDRAM內(nèi)存模塊 |

| 文件頁數(shù): | 13/39頁 |

| 文件大小: | 1036K |

| 代理商: | HYS72D32500GR-7-B |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁當(dāng)前第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁

HYS72D[128/64/32]5[00/20/21]GR–[7F/7/8]-B

Registered DDR SDRAM-Modules

Pin Configuration

Data Sheet

13

Rev. 1.03 2004-01

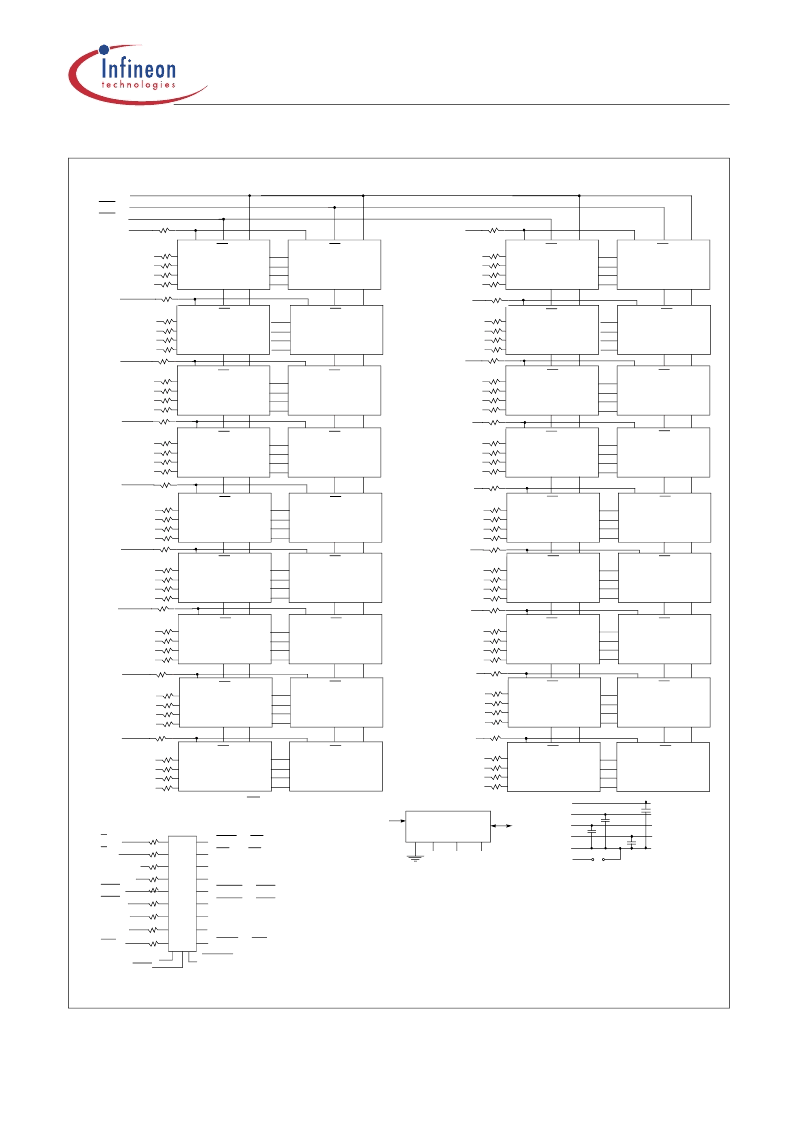

Figure 3

Block Diagram: Two Ranks 128M

×

72 DDR SDRAM DIMM Modules (

×

4 components)

HYS72D128520GR on Raw Card N

PCK

PCK

RS0

DQS0

DQS4

DQS6

DQS2

DQ0

DQ1

DQ2

DQ3

DQ8

DQ9

DQ10

DQ11

DQ16

DQ17

DQ18

DQ19

DQ24

DQ25

DQ26

DQ27

DQ32

DQ33

DQ34

DQ35

DQ40

DQ41

DQ42

DQ43

DQ56

DQ57

DQ58

DQ59

I/DQS

I/O 1

I/O 2

I/O 3

D0

DQS

I/O 0

I/O 1

I/O 2

I/O 3

I/DQS

I/O 1

I/O 2

I/O 3

DQS

I/O 0

I/O 1

I/O 2

I/O 3

DQS

I/O 0

I/O 1

I/O 2

I/O 3

DQS

I/O 0

I/O 1

I/O 2

I/O 3

DQS

I/O 0

I/O 1

I/O 2

I/O 3

D1

D2

D3

D4

D5

D7

DQ48

DQ49

DQ50

DQ51

DQS

D6

DQ4

DQ5

DQ6

DQ7

DQ12

DQ13

DQ14

DQ15

DQ20

DQ21

DQ22

DQ23

DQ28

DQ29

DQ30

DQ31

DQ36

DQ37

DQ38

DQ39

DQ44

DQ45

DQ46

DQ47

DQ60

DQ61

DQ62

DQ63

DQS

I/O 0

I/O 1

I/O 2

I/O 3

D9

DQS

I/O 0

I/O 1

I/O 2

I/O 3

DQS

I/O 0

I/O 1

I/O 2

I/O 3

DQS

I/O 0

I/O 1

I/O 2

I/O 3

DQS

I/O 0

I/O 1

I/O 2

I/O 3

DQS

I/O 0

I/O 1

I/O 2

I/O 3

DQS

I/O 0

I/O 1

I/O 2

I/O 3

DM0/DQS9

D10

D11

D12

D13

D14

D16

DQ52

DQ53

DQ54

DQ55

DQS

I/O 0

I/O 1

I/O 2

I/O 3

D15

CK0, CK0 --------- PLL*

S

S

S

S

S

S

S

S

S

S

S

S

S

S

S

S

S1

BA0-BA1

A0-A13

RAS

CAS

CKE0

CKE1

RS1 -> S : SDRAMs D18-D35

RBA0-RBA1 -> BA0-BA1: SDRAMs D0-D35

RA0-RA13 -> A0-A13: SDRAMs D0- D35

RRAS -> RAS: SDRAMs D0-D35

RCAS -> CAS: SDRAMs D0-D35

RCKE0 -> CKE: SDRAMs D0-D17

S0

RSO -> S : SDRAMs D0-D17

V

SS

RS1

DQS1

DQS3

DM

DM

DM

DM

DM

DM

DM

DM

DM

DM

DM

DM

DM

DM

DM

DM

DQS5

DQS7

DM6/DQS15

DM5/DQS14

DM4/DQS13

DM1/DQS10

DM2/DQS11

DM3/DQS12

DM7/DQS16

* Wire per Clock Loading Table/Wiring Diagrams

V

DD

VREF

V

SS

V

DDID

D0-D35

D0-D35

D0-D35

V

DDQ

D0-D35

Notes:

1. DQ-to-I/O wiring may be changed within a byte.

2. DQ/DQS/DM/CKE/S relationships must be maintained as shown.

3. DQ/DQS resistors should be 22 Ohms.

4. V

DDID

strap connections (for memory device V

DD

, V

DDQ

):

STRAP OUT (OPEN): V

DD

= V

DDQ

STRAP IN (V

SS

): V

DD

≠

V

DDQ

.

5. Address and control resistors should be 22 Ohms.

6. Each Chip Select and CKE pair alternate between decks for ther-

mal enhancement.

Strap: see Note 4

WE

RWE -> WE: SDRAMs D0-D35

R

E

G

I

S

T

E

R

DQS

I/O 3

I/O 2

I/O 1

I/O 0

D18

DQS

I/O 0

I/O 1

I/O 2

I/O 3

DQS

I/O 0

I/O 1

I/O 2

I/O 3

DQS

I/O 0

I/O 1

I/O 2

I/O 3

DQS

I/O 0

I/O 1

I/O 2

I/O 3

DQS

I/O 0

I/O 1

I/O 2

I/O 3

DQS

I/O 0

I/O 1

I/O 2

I/O 3

D19

D20

D21

D22

D23

D25

S

S

S

S

S

S

S

DM

DM

DM

DM

DM

DM

DM

DM

DQS

I/O 0

I/O 1

I/O 2

I/O 3

D27

DQS

I/O 0

I/O 1

I/O 2

I/O 3

DQS

I/O 0

I/O 1

I/O 2

I/O 3

DQS

I/O 0

I/O 1

I/O 2

I/O 3

DQS

I/O 0

I/O 1

I/O 2

I/O 3

DQS

I/O 0

I/O 1

I/O 2

I/O 3

DQS

I/O 0

I/O 1

I/O 2

I/O 3

D28

D29

D30

D31

D32

D34

DQS

I/O 0

I/O 1

I/O 2

I/O 3

D33

S

S

S

S

S

S

S

S

DM

DM

DM

DM

DM

DM

DM

DM

CB0

CB1

CB2

CB3

I/DQS

I/O 1

I/O 2

I/O 3

D8

S

DM

DQS8

DQS

I/O 0

I/O 1

I/O 2

I/O 3

D26

S

DM

CB4

CB5

CB6

CB7

DQS

I/O 0

I/O 1

I/O 2

I/O 3

D17

S

DM

DM8/DQS17

DQS

I/O 0

I/O 1

I/O 2

I/O 3

D35

S

DM

RESET

RCKE1 -> CKE: SDRAMs D18-D35

I/O 0

I/O 1

I/O 2

I/O 3

I/O 0

I/O 1

I/O 2

I/O 3

V

DDSPD

Serial PD

A0

Serial PD

A1

A2

SA0 SA1 SA2

SDA

SCL

WP

S

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYS72D64500GR-7-B | Registered DDR SDRAM-Modules |

| HYS72D128520GR-7-B | Registered DDR SDRAM-Modules |

| HYS72D128520GR-7F-B | Connector Wall Plate; Color:Almond; Leaded Process Compatible:Yes; No. of Ports:2 RoHS Compliant: Yes |

| HYS72D128521GR-7-B | Connector Wall Plate; Color:Electric White; Leaded Process Compatible:Yes; No. of Ports:4 RoHS Compliant: Yes |

| HYS72D32500GR-8-B | Registered DDR SDRAM-Modules |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYS72D32500GR-7F-B | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:Registered DDR SDRAM-Modules |

| HYS72D32500GR-8 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x72 SDRAM Module |

| HYS72D32500GR-8-A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:?256MB (32Mx72) PC1600 1-bank? |

| HYS72D32500GR-8-B | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:Low Profile Registered DDR-I SDRAM-Modules |

| HYS72D32501GR-7 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x72 SDRAM Module |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。